Apple /// Computer Information • Doc # 78 • ProFile Hard Disk Repair Info

## Apple /// Computer Information

APPLE /// PROFILE HARD DISK REPAIR DOCUMENTS

78

Ex Libris David T. Craig

SCANNED BY JOE D VOGEL -- 7/2006

Source: David T. Craig Page 0001 of 0580

Apple Computer, Inc. Service Engineering Department

# Apple /// Computer Repair Documents

DAVID T. CRAIG

736 EDGEWATER, WICHITA, KANSAS 67230 [USA]

71533.606@ COMPUSERVE. COM

Source: David T. Craig Page 0002 of 0580

Page lof1

#### APPLE/// COMPUTER

#### REPAIR INFORMATION: PROFILEHARD DISK

[ DAVID T. CRAIG - 736 EDGEWATER, WICHITA, KANSAS 67230 U.S.A. ]

#### TABLE OF CONTENTS

| #                                      | PGS | TITLE                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>3</b> 1                             | 8   | PROFILE SALES KIT: PROFILE TECHNICAL REVIEW                                                                                                                                                                                                                                                                                                                                                                         |

| 12-2                                   | 6   | APPLE /// PROFILE LIMITED DATA RECOVERY                                                                                                                                                                                                                                                                                                                                                                             |

| <b>20</b> 3                            | 11  | PROFILE EXCHANGE PROCEDURES                                                                                                                                                                                                                                                                                                                                                                                         |

| 324                                    | 238 | PROFILE LEVEL 2 PHASE 1 SERVICE MANUAL (PRELIMINARY)                                                                                                                                                                                                                                                                                                                                                                |

| 2715                                   | 101 | PROFILE LEVEL 2 PHASE 1 SERVICE MANUAL (VERY PRELIMINARY)                                                                                                                                                                                                                                                                                                                                                           |

| 372 6                                  | 26  | DSKDBG - BLOCK DEVICE DEBUGGER (VERSION E00.17) SERVICE MANUAL                                                                                                                                                                                                                                                                                                                                                      |

| 399 7                                  | 1   | HOW TO USE THE REV 18 DEBUGGER TO COPY PROFILES                                                                                                                                                                                                                                                                                                                                                                     |

| 4018                                   | 6   | HOW TO USE THE REV 18 DEBUGGER TO COPY PROFILES  PROFILE PRODUCTION FORMAT TEST PROCEDURE WITH APPLE ///  CONVERTING A 5M BYTE PROFILE TO 10M BYTE  PROFILE CERTIFICATION AND FAILURE CRITERIA  PROFILE DEBUG DATA STATUS BYTE DEFINITIONS  PROFILE POWER SUPPLY (CLASS B) SPECIFICATION  PROFILE POWER SUPPLY (CLASS A2 - INTERNATIONAL) SPECIFICATION  HEAD DISK ASSEMBLY SPECIFICATION (FROM SEAGATE TECHNOLOGY) |

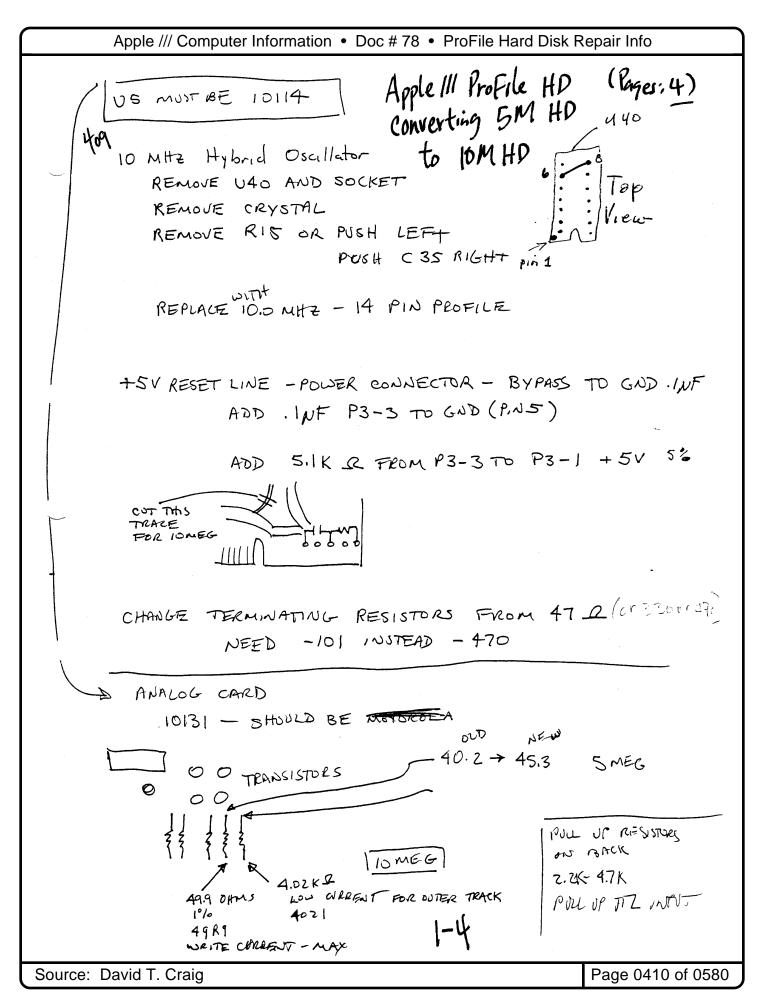

| 408 9                                  | 4   | CONVERTING A 5M BYTE PROFILE TO 10M BYTE                                                                                                                                                                                                                                                                                                                                                                            |

| 413 10                                 | 2   | PROFILE CERTIFICATION AND FAILURE CRITERIA                                                                                                                                                                                                                                                                                                                                                                          |

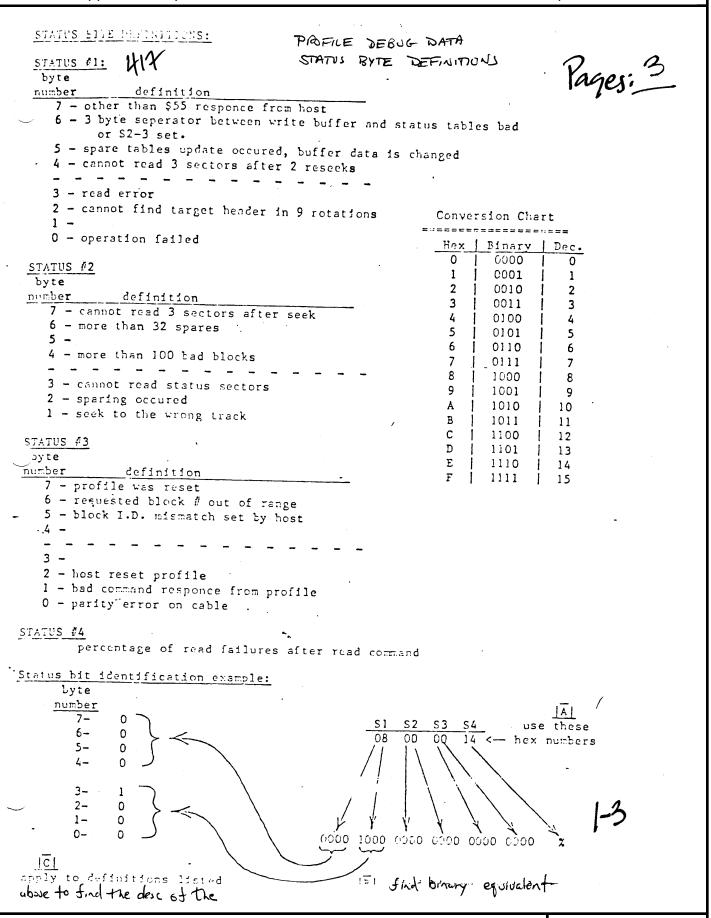

| 416 11                                 | 3   | PROFILE DEBUG DATA STATUS BYTE DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                          |

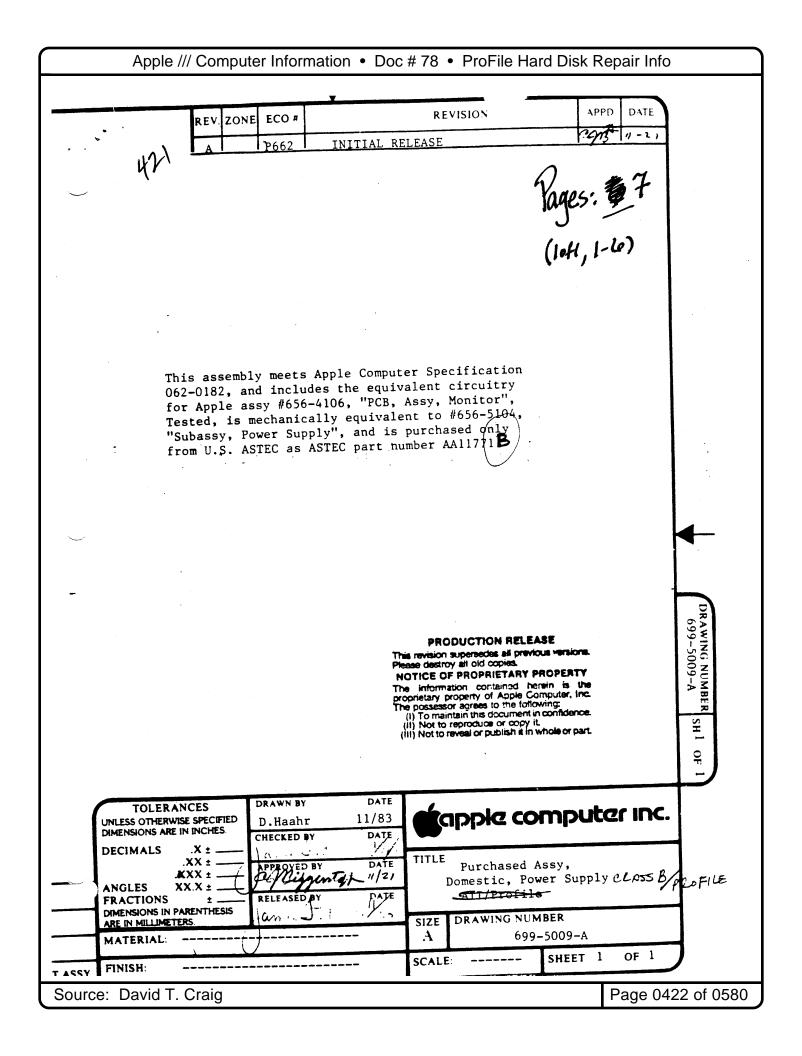

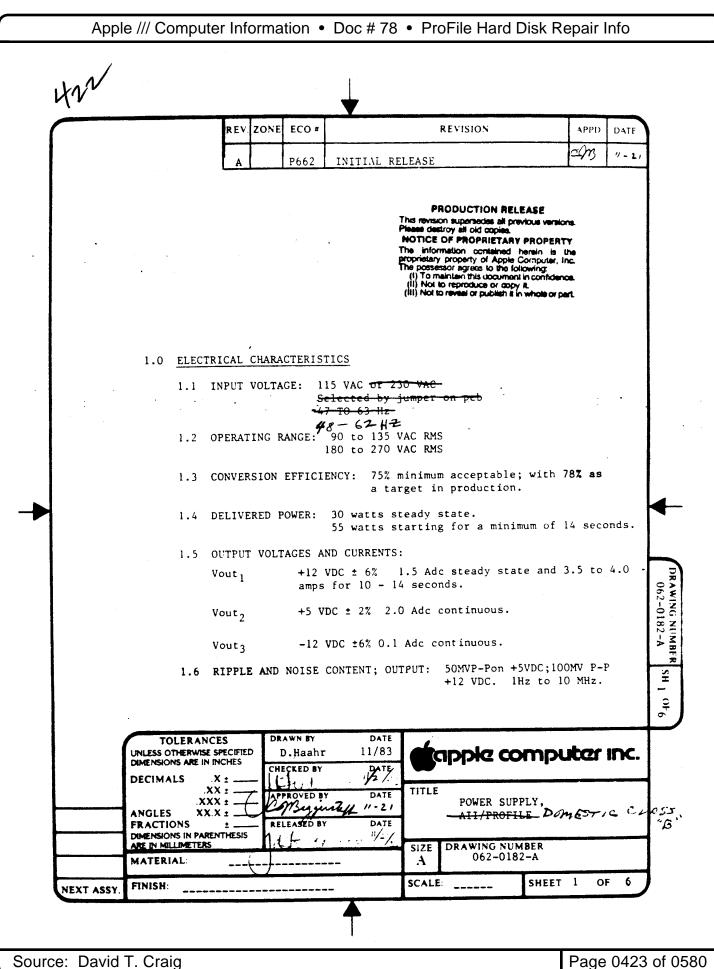

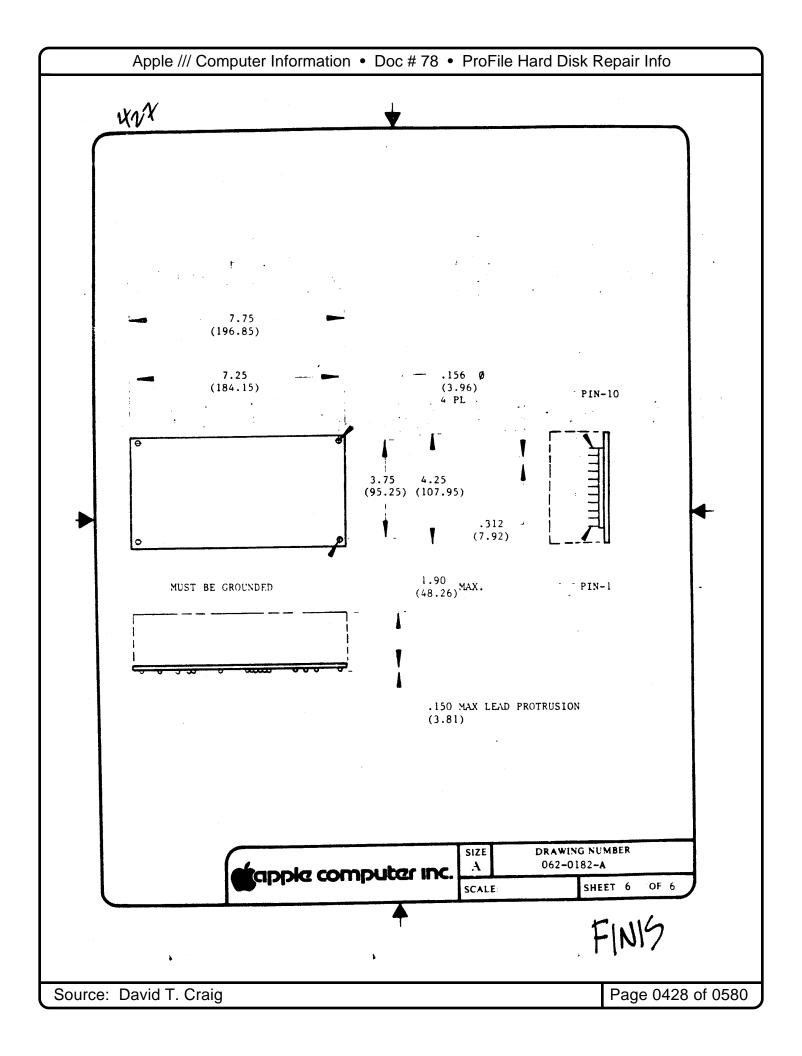

| 420 12                                 | 7   | PROFILE POWER SUPPLY (CLASS B) SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                        |

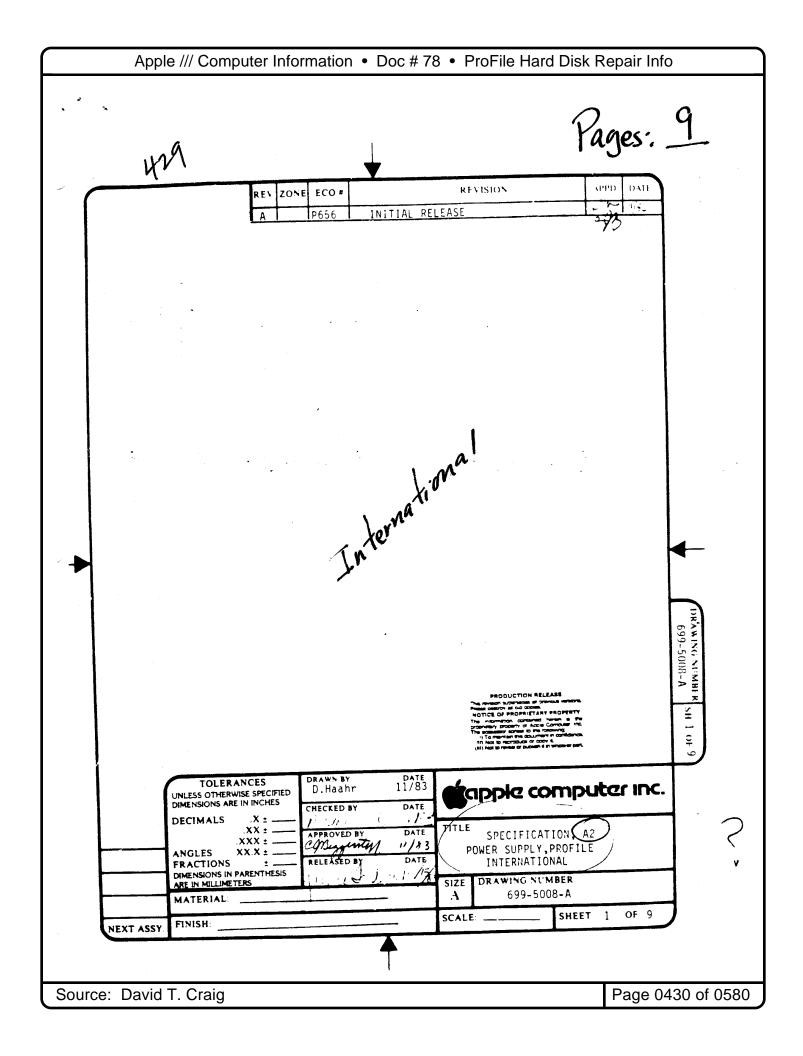

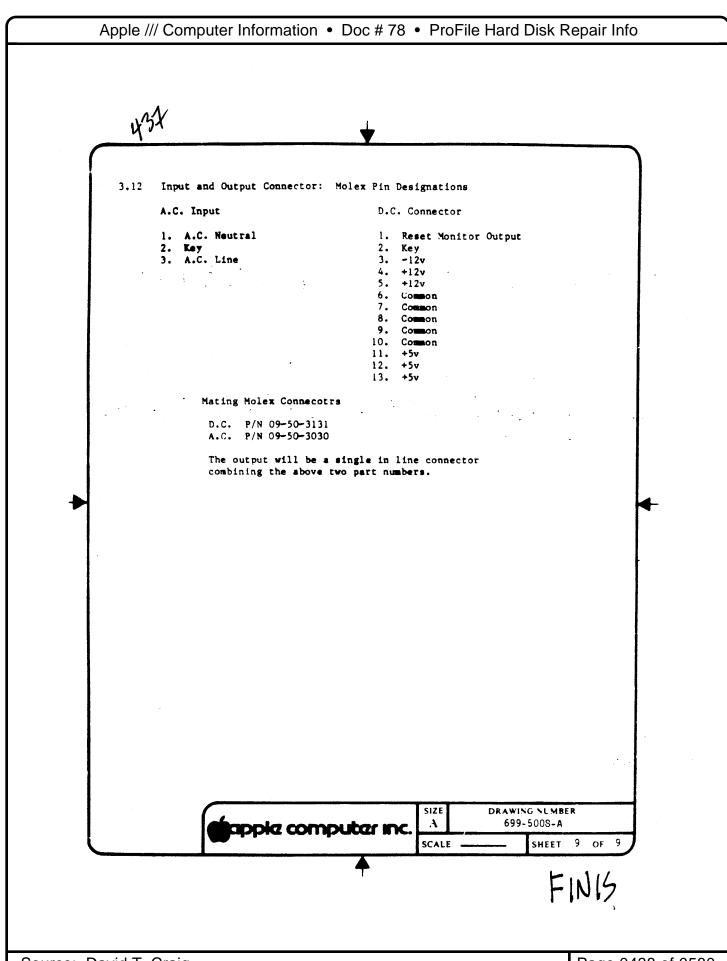

| <b>428</b> 13                          | 9   | PROFILE POWER SUPPLY (CLASS A2 - INTERNATIONAL) SPECIFICATION \ 5 T \                                                                                                                                                                                                                                                                                                                                               |

| <b>43</b> 8 14                         | 12  |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 451 15                                 | 9   |                                                                                                                                                                                                                                                                                                                                                                                                                     |

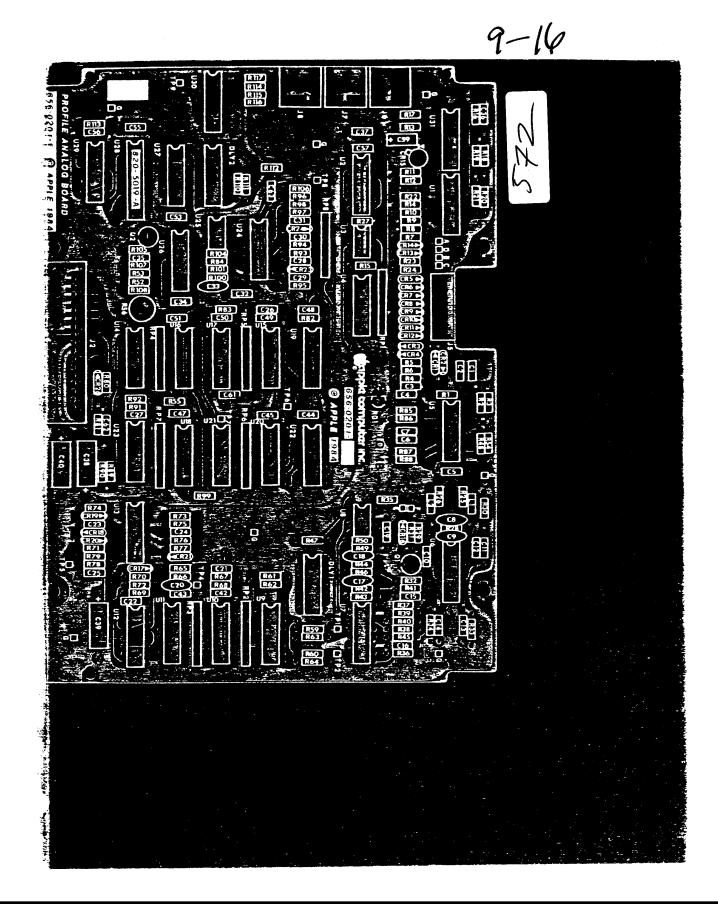

| 461 16                                 |     | PROFILE ANALOG BOARD FUNCTIONAL TEST (05 JAN 1984)                                                                                                                                                                                                                                                                                                                                                                  |

| 468 17                                 |     | PROFILE ANALOG BOARD DEBUG TEST (08 DEC 1983)                                                                                                                                                                                                                                                                                                                                                                       |

| 472 18                                 | 1   | PROFILE ANALOG BOARD DEBUG TEST REPAIR NOTES (08 DEC 1983)                                                                                                                                                                                                                                                                                                                                                          |

| 474 19                                 |     | PROFILE ANALOG BOARD UPGRADE                                                                                                                                                                                                                                                                                                                                                                                        |

| 477 20                                 |     | PROFILE INTERFACE BOARD TESTER OPERATION AND MAINTENANCE MANUAL                                                                                                                                                                                                                                                                                                                                                     |

| 486 21                                 | 21  |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 508 22                                 |     | FORMATTING THE PROFILE HDA                                                                                                                                                                                                                                                                                                                                                                                          |

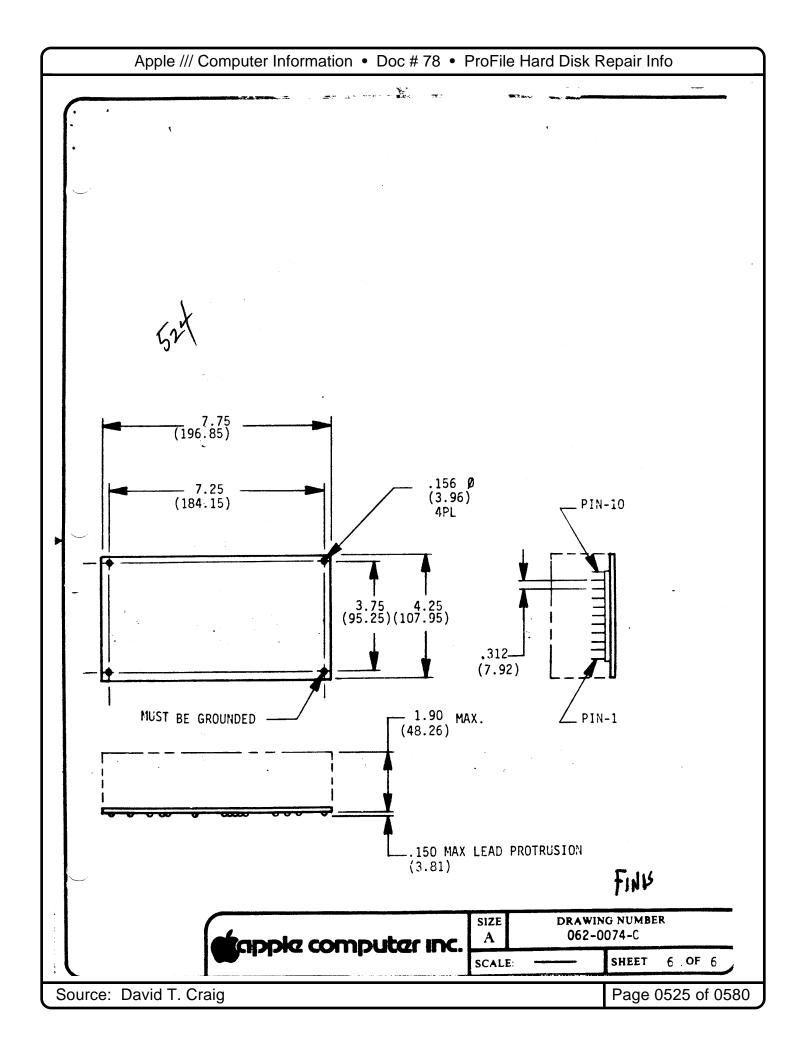

| 517 23                                 | 7   |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| J25 24                                 |     | PROFILE SECTOR INTERLEAVE CHARTS PROFILE STATUS INFORMATION                                                                                                                                                                                                                                                                                                                                                         |

| 528 25<br>531 26                       |     | MISC. PROFILE OSCILLOSCOPE CHARTS                                                                                                                                                                                                                                                                                                                                                                                   |

| 591 28<br>537 27                       |     | PROFILE CONTROLLER ROM MISC. FACTS                                                                                                                                                                                                                                                                                                                                                                                  |

| 539 <sup>28</sup>                      | 4   |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 534 29<br>544 29                       | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 544 <sup>27</sup><br>546 <sup>30</sup> |     | PROFILE FORMAT AND DIAGNOSTIC PROGRAM (VERSION 0.11) (PRELIMINARY)                                                                                                                                                                                                                                                                                                                                                  |

| 553 31                                 |     | SOS SOFTWARE DRIVER INFORMATION                                                                                                                                                                                                                                                                                                                                                                                     |

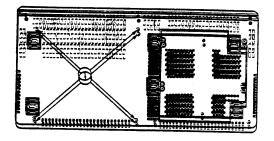

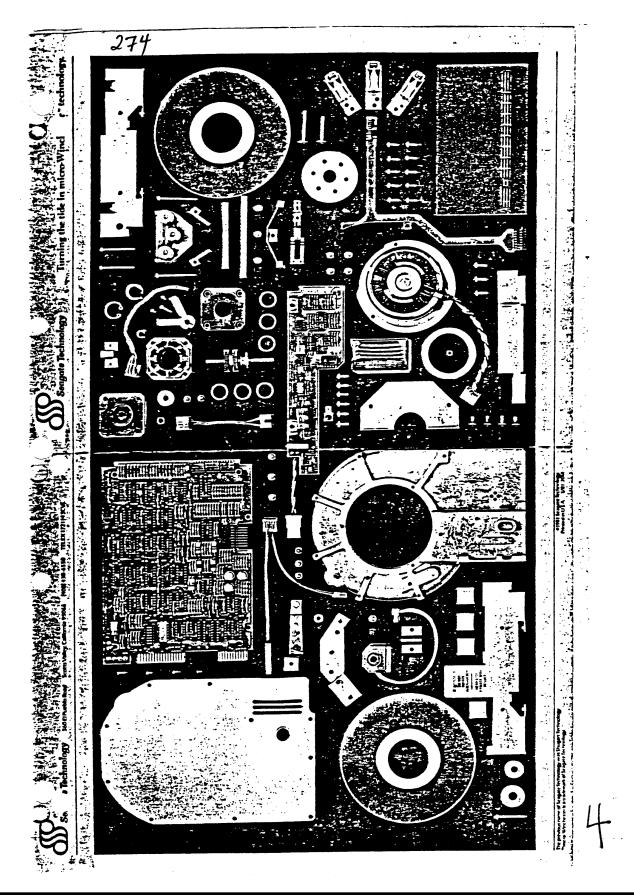

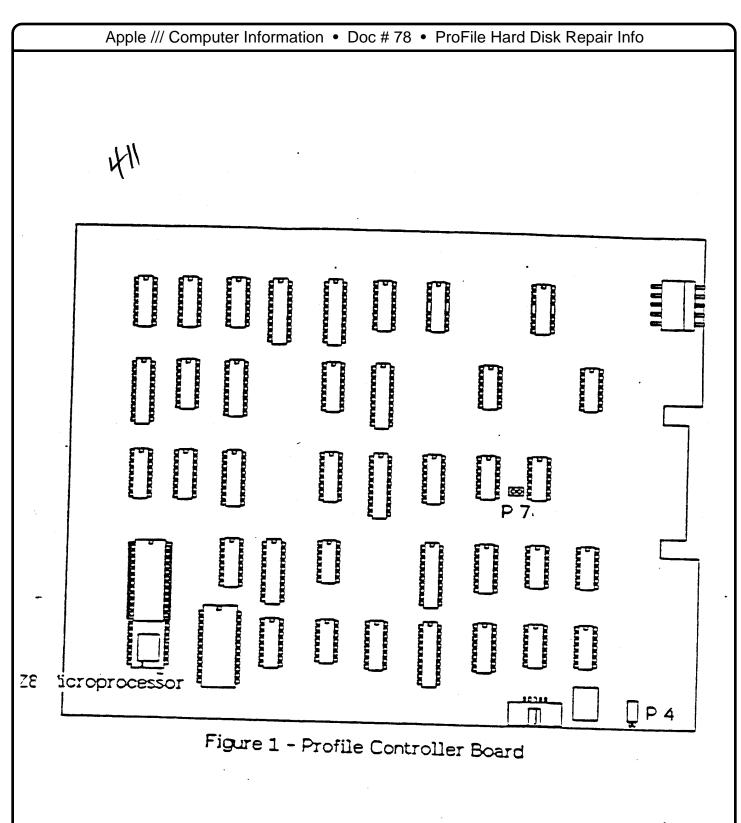

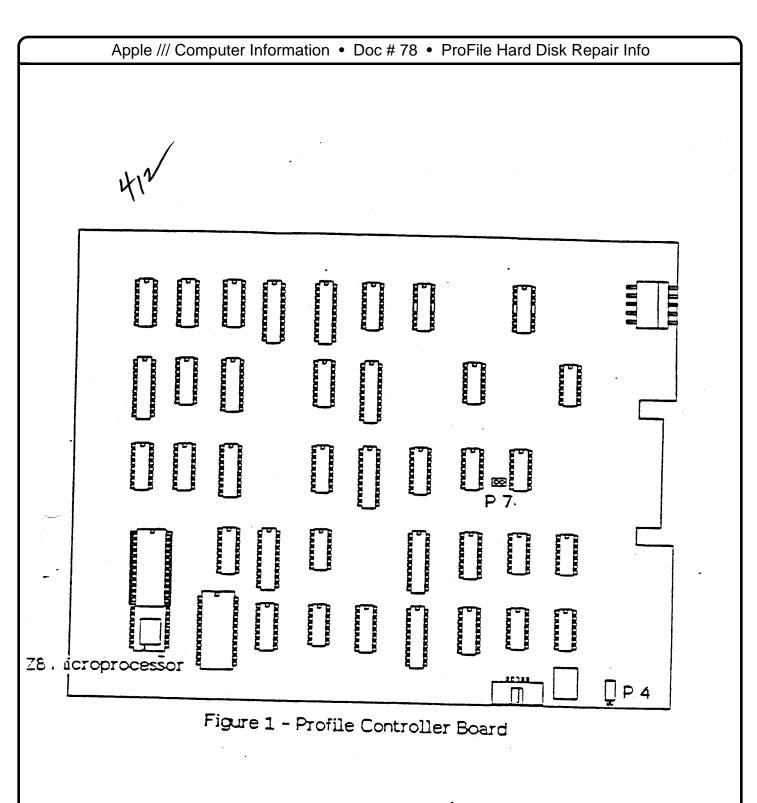

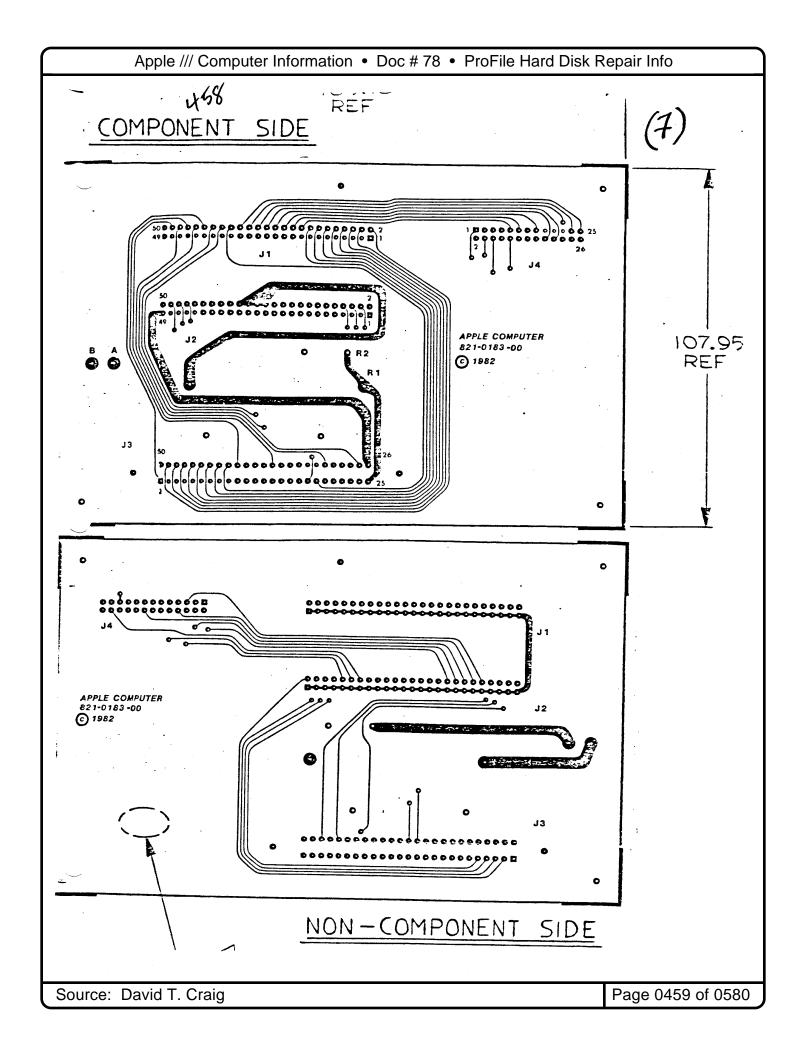

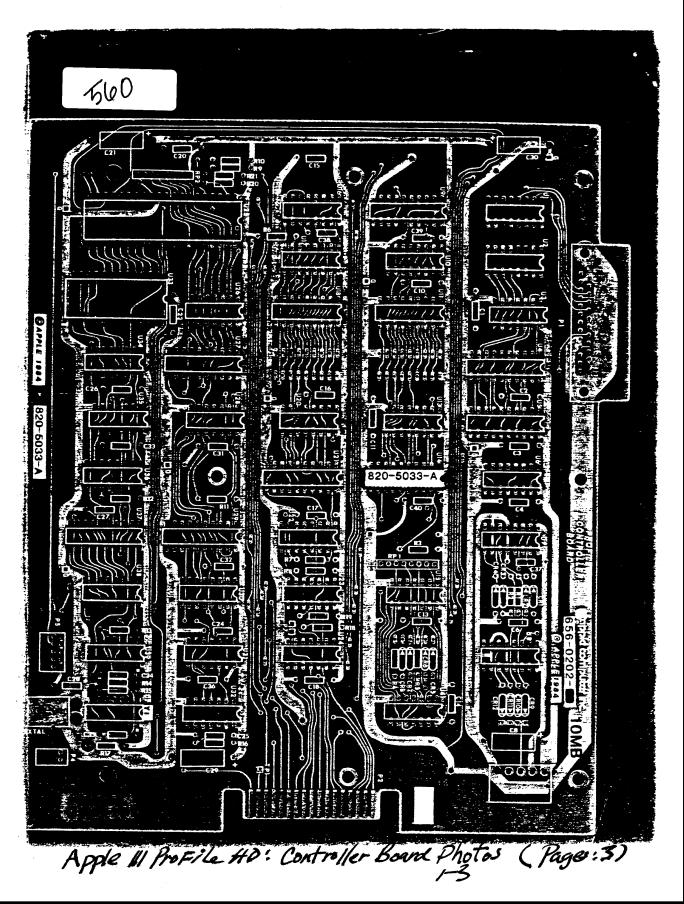

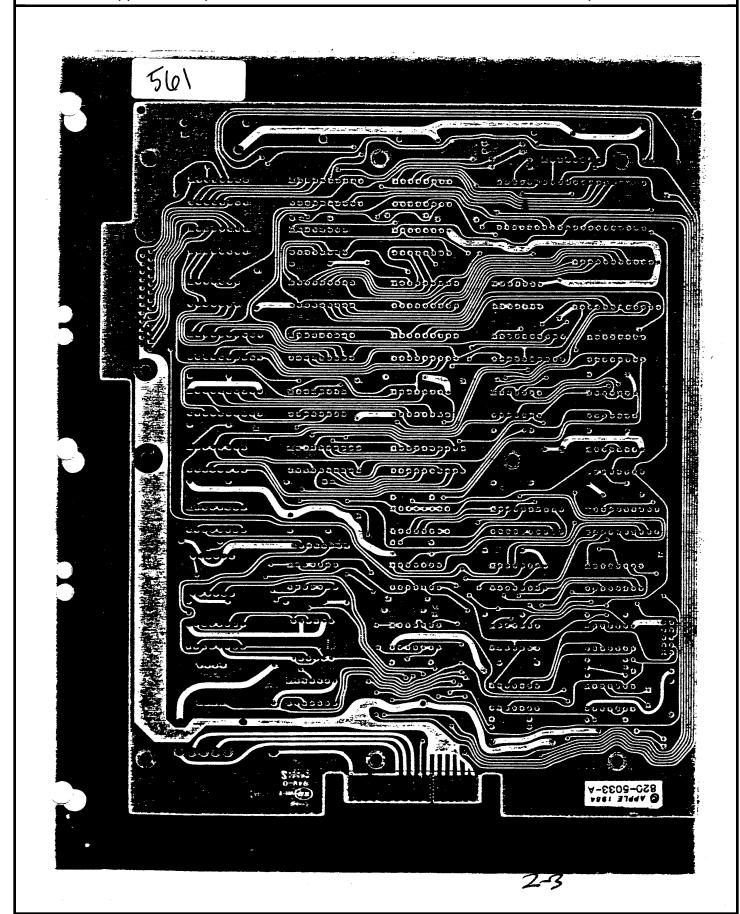

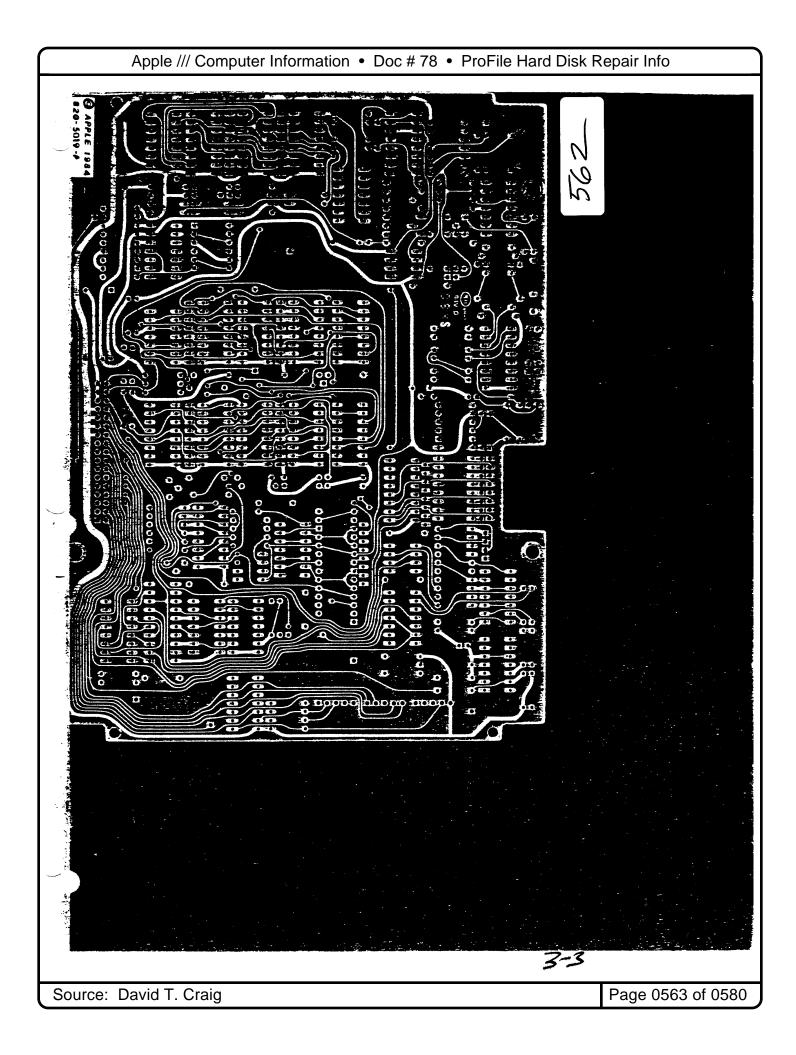

| 559 32                                 | 3   | PROFILE CONTROLLER BOARD PHOTOS                                                                                                                                                                                                                                                                                                                                                                                     |

| 5103 33                                | 16  |                                                                                                                                                                                                                                                                                                                                                                                                                     |

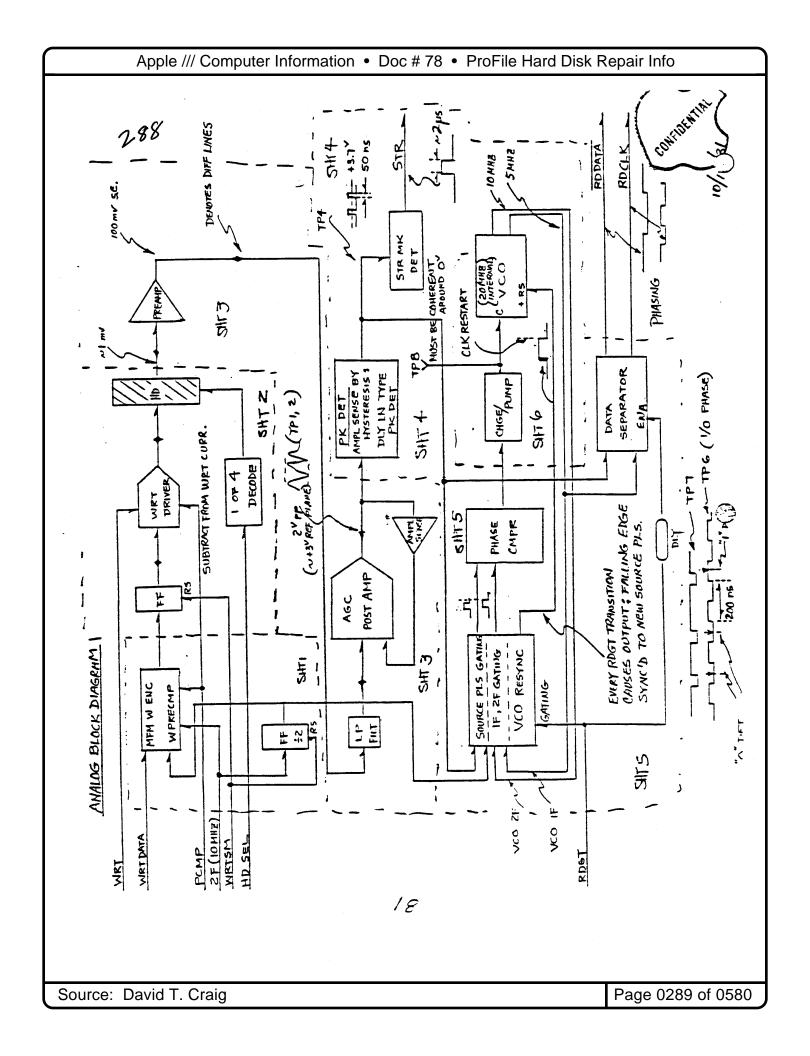

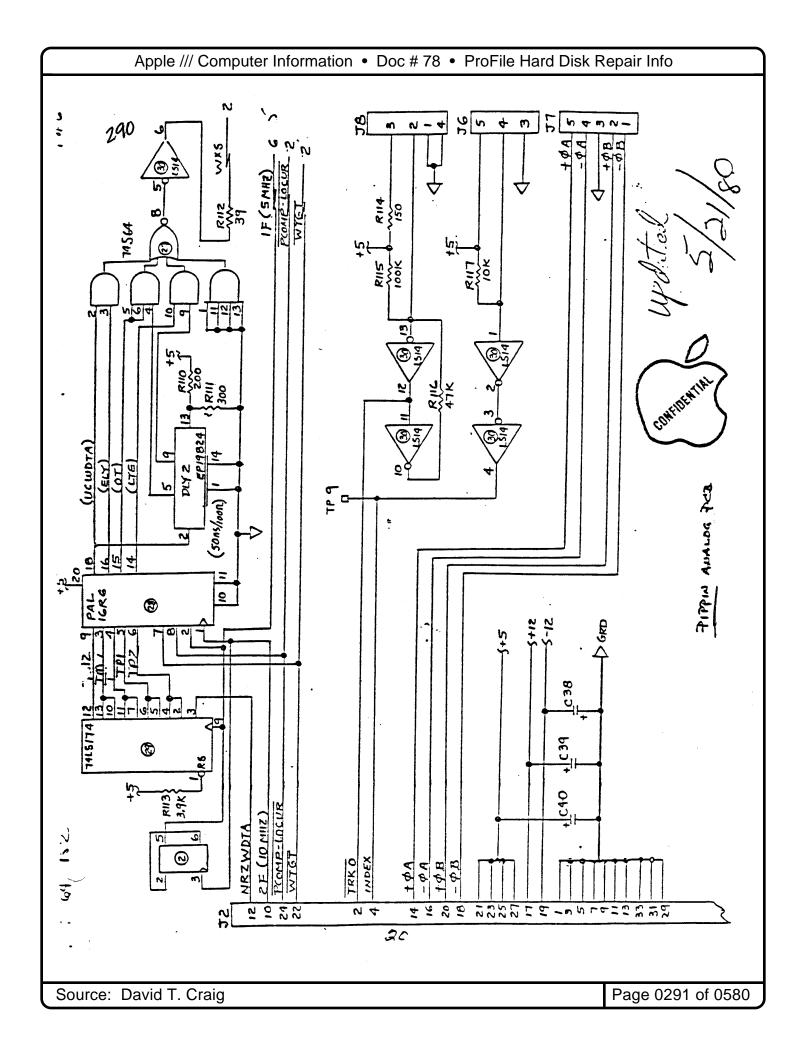

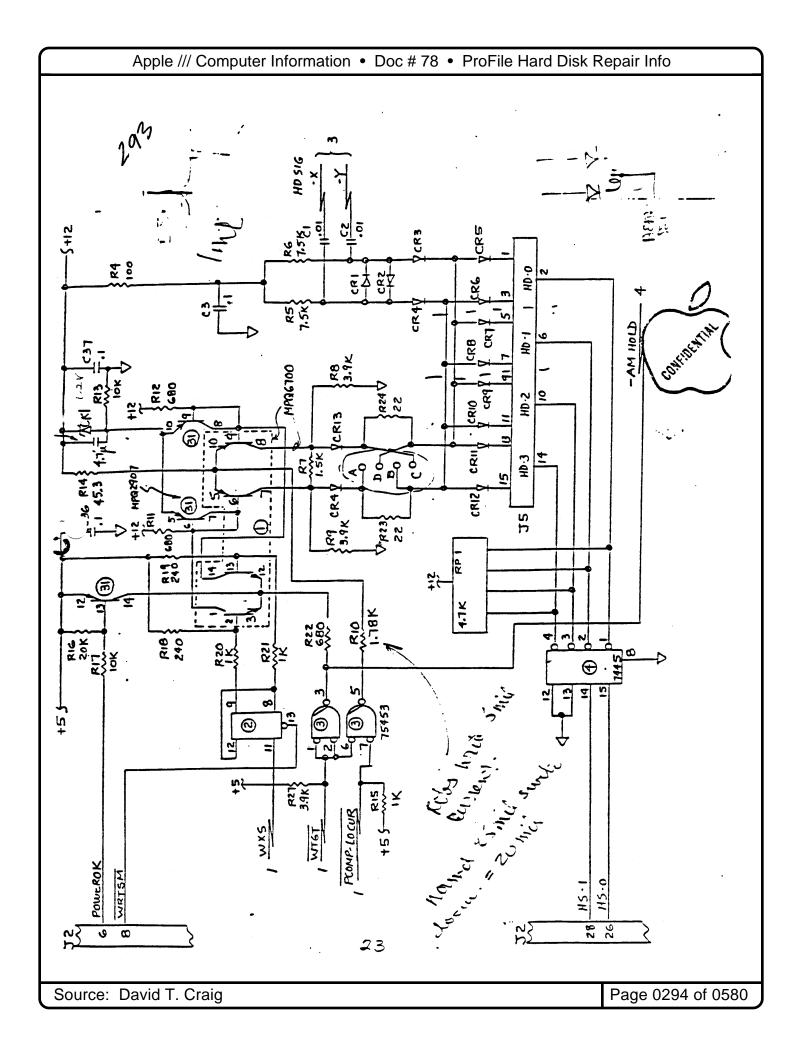

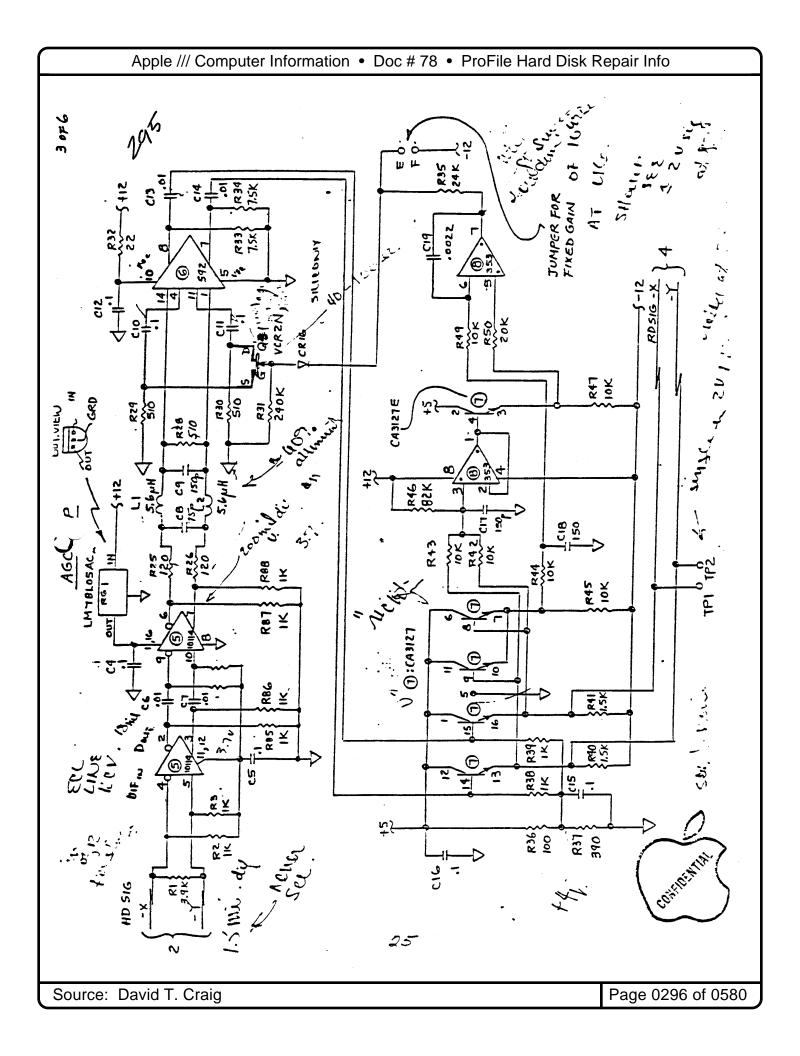

563 33 16 FUNCTIONAL DESCRIPTION OF THE PROFILE ANALOG BOARD (ROUGH DRAFT)

Source: David T. Craig Page 0003 of 0580

Apple Computer, Inc. Service Engineering Department

## Apple /// Computer Repair Document

COMPONENT NAME

Profile Hard Pisk

DOCUMENT TITLE

ProFile Sales Kit: ProFile Technical Review

Author: Apple

DAVID T. CRAIG 736 EDGEWATER, WICHITA, KANSAS 67230 [USA]

Source: David T. Craig Page 0004 of 0580

Apple III

#### ProFile Sales Kit

#### ProFile Technical Review

This section of the ProFile Sales Kit will give you an overview of the technical details of the ProFile Personal Mass Storage System for the Apple ///. It is intended to be a summary only, and is not a detailed explanation of the engineering aspects of the ProFile. This information is presented to give you a better understanding of the quality, reliability, and performance that Apple has built into ProFile, and to prepare you to answer technical questions raised by your customers. Additional information regarding the ProFile can be found in "Section D" of this Sales Kit.

#### What is ProFile?

Profile is a Winchester technology hard disk drive designed to operate with the Apple /// personal computer. It has a formatted storage capacity of 5 Megabytes, which is essentially the same as 35 floppy disks (the Apple /// disk drive uses floppies that have a capacity of 140K Bytes). The Profile will, as you can see, enable you to store large amounts of data on a single device. You are also able to store files that are larger than the 140K floppies that you usually use. In addition, you are able to access your data much faster with the Profile than with the Disk ///.

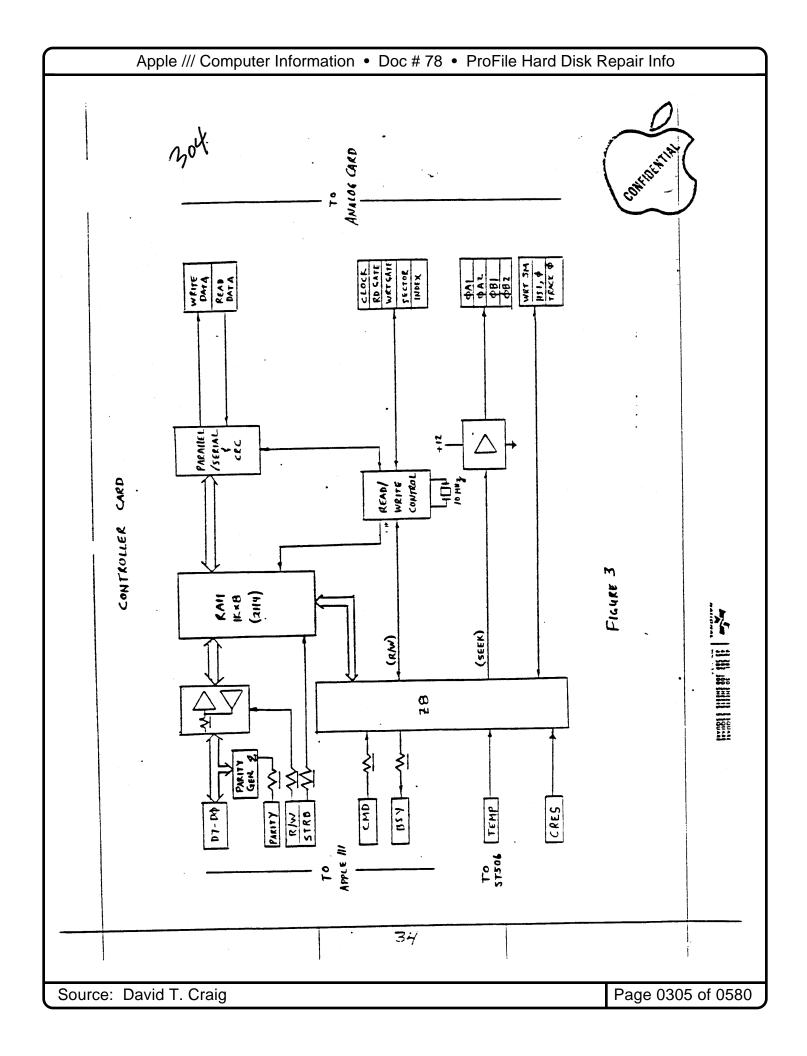

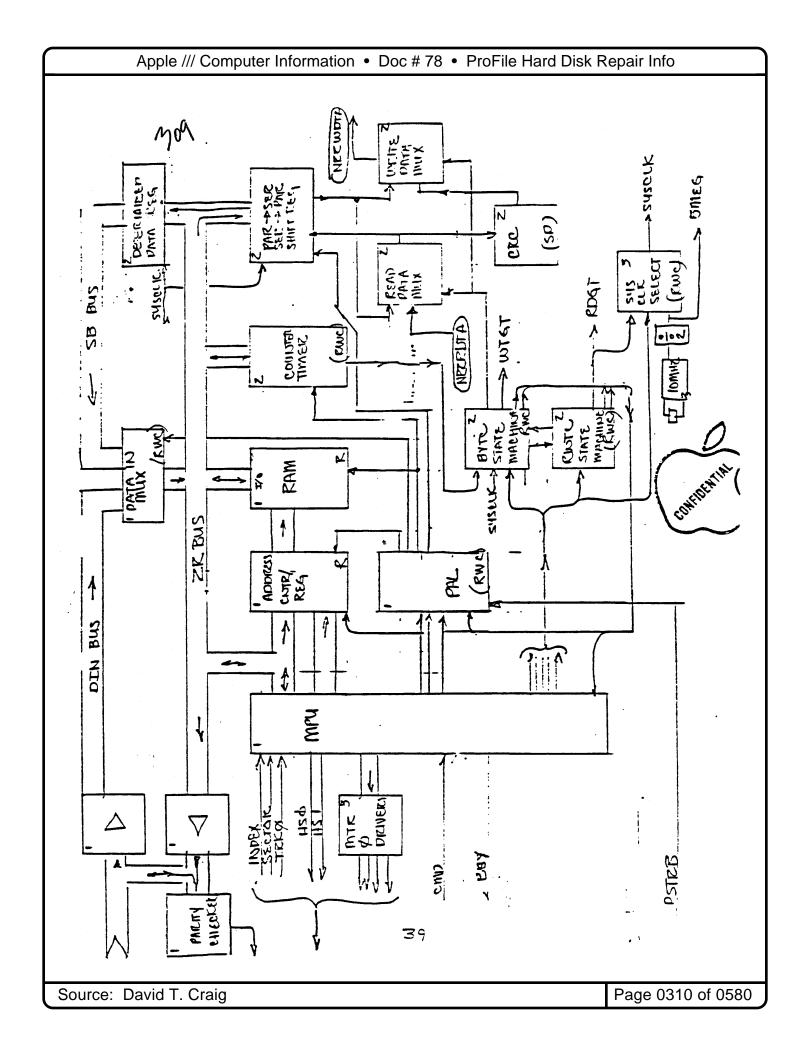

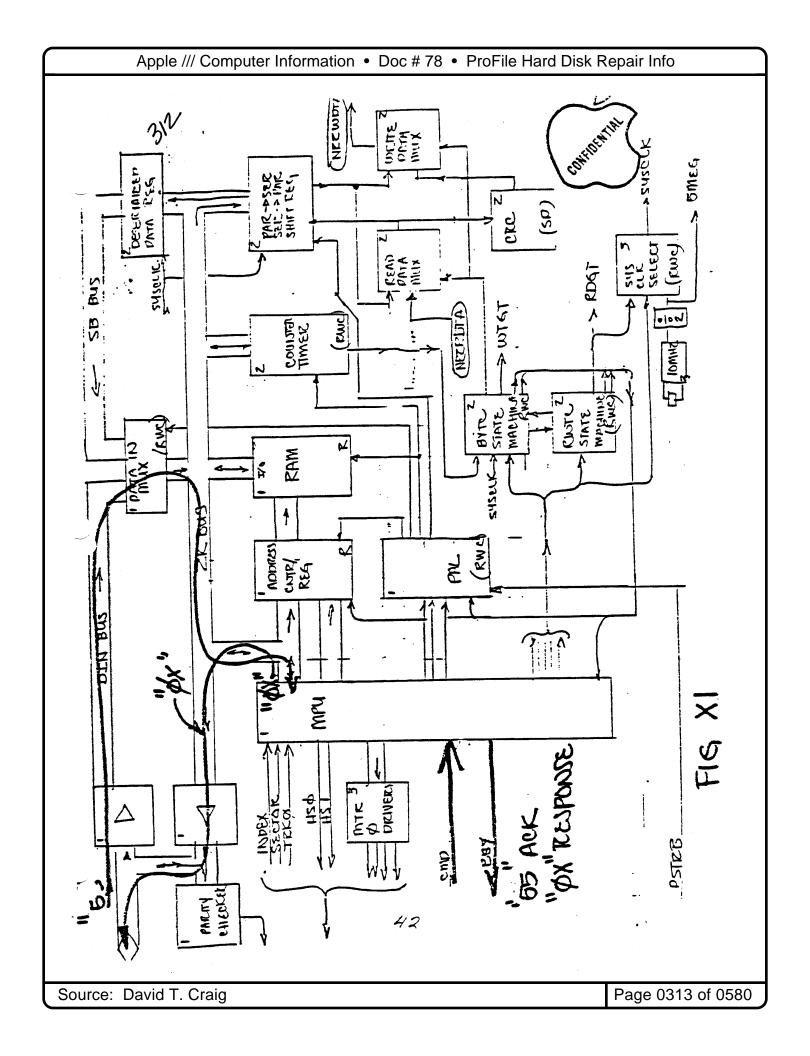

The ProFile physically consists of three main assemblies. They are the ProFile drive, the Apple /// interface card, and the interconnect cable. The ProFile has its own power supply, and as such does not rely on the Apple /// for operating power. Functionally, the ProFile consists of five major modules:

- 1. The Controller Card

- 2. The Power Supply

- 3. The Analog Card

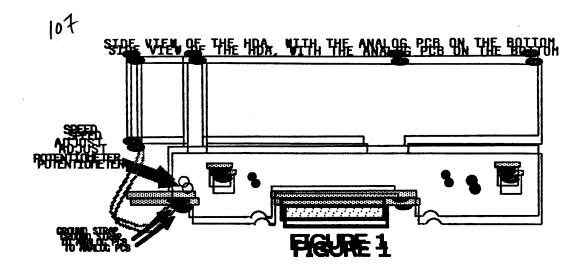

- 4. The Head Disk Assembly (HDA) with motor control board

- 5. The Interface Card

The following sections describe the function of these modules in detail.

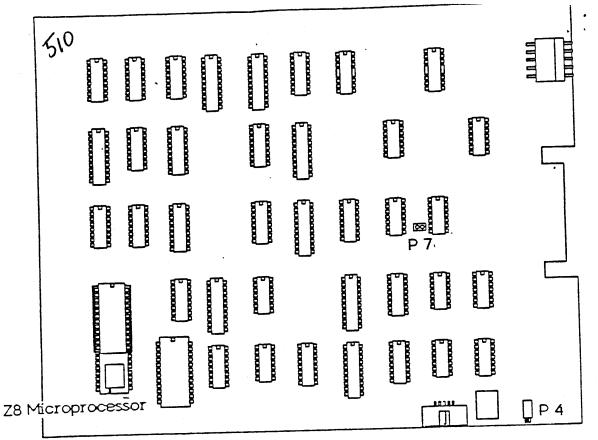

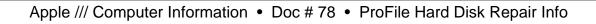

#### The Contoller Card

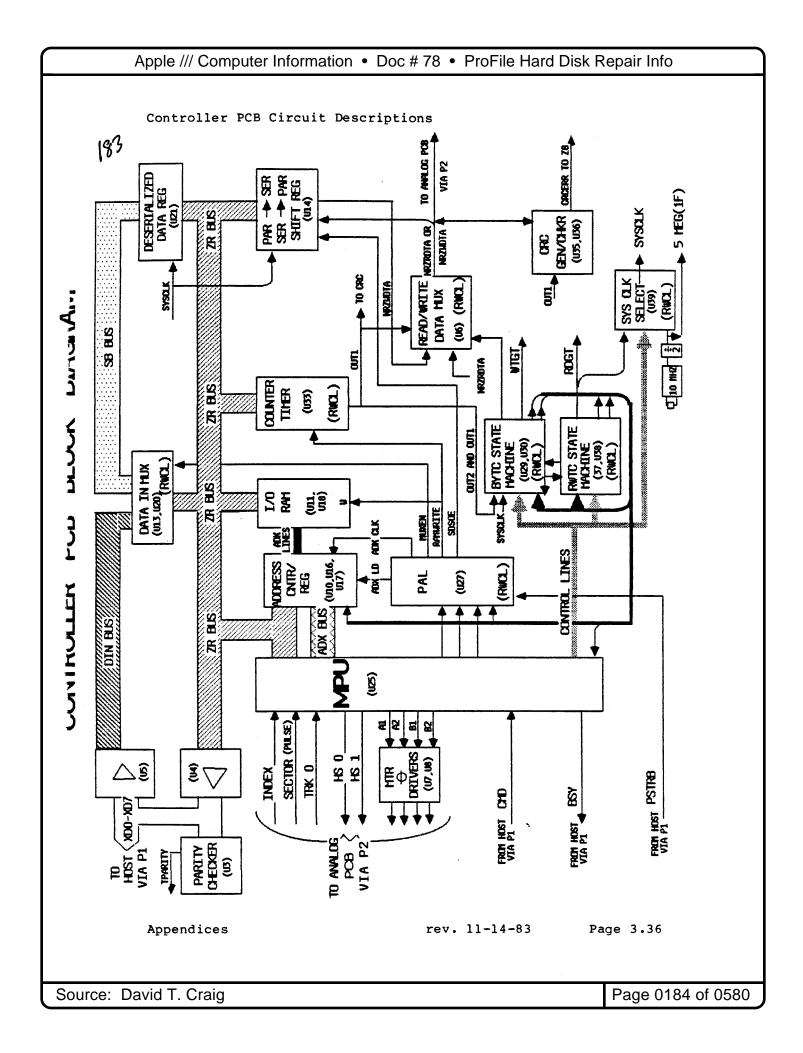

Functionally, the controller provides communications with the Apple ///, provides signals to read and write serial data on the disk, moves the heads to the proper track, and monitors error conditions. The controller consists of a Z8 microprocessor, 2K bytes of RAM, error detection logic, and read/write control logic.

1-8

Source: David T. Craig

The Z8 provides an intelligent interface to the Apple ///. High level commands, such as read, write, and status, are passed to the Z8 through the RAM. The Z8 executes the command and passes the result of the operation back to the Apple /// through the RAM.

The controller also interfaces to the analog card to pass head control information to it. In this way the controller determines when read/write operations will take place. The Z8 controls the stepper motor to move the heads from track to track (called "seeking"), selects one of four read/write heads, and writes sector marks on the disk during formatting.

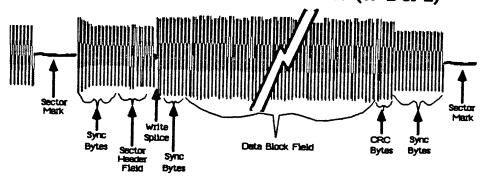

Read /Write functions are performed by the read/write logic on command from the Z8. This logic in turn controls the parallel to serial data conversion when writing, and the serial to parallel data conversion when reading. To ensure the proper transfer of data, the controller does a CRC (cyclic redundancy check) of the serial data. If an error occurs, the Z8 will automatically perform an error recovery routine and try to relocate the data onto a different section of the disk. The sector causing problems will be removed from use to prevent future errors.

To prevent heat build-up in the drive, the Z8 removes power from the stepper motor if no commands have been received for 0.75 seconds. After 3 seconds, the head is moved to a non data area of the disk to prevent accidental damage to data if a failure (such as power loss) occurs. The READY light on the front of the ProFile is lit whenever the controller is idle (not busy).

#### Power Supply

The power supply provides the +5VDC, +12VDC, and -12VDC needed by the ProFile for operation. The supply also contains monitoring circuitry to detect a power failure. Once a failure is detected, the head current is shut off to prevent the accidental writing of false data that would otherwise occur if a write operation were in process when the power failed. The power supply is completely shielded to eliminate the effects of electro magnetic radiation.

#### Analog Card

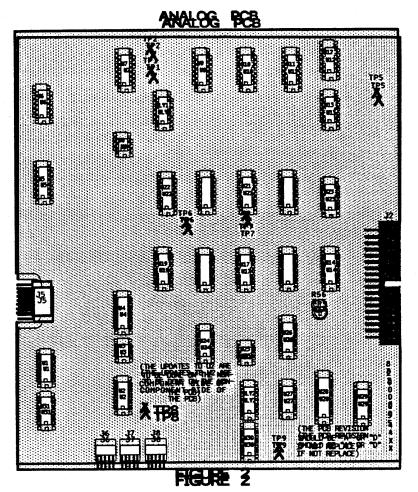

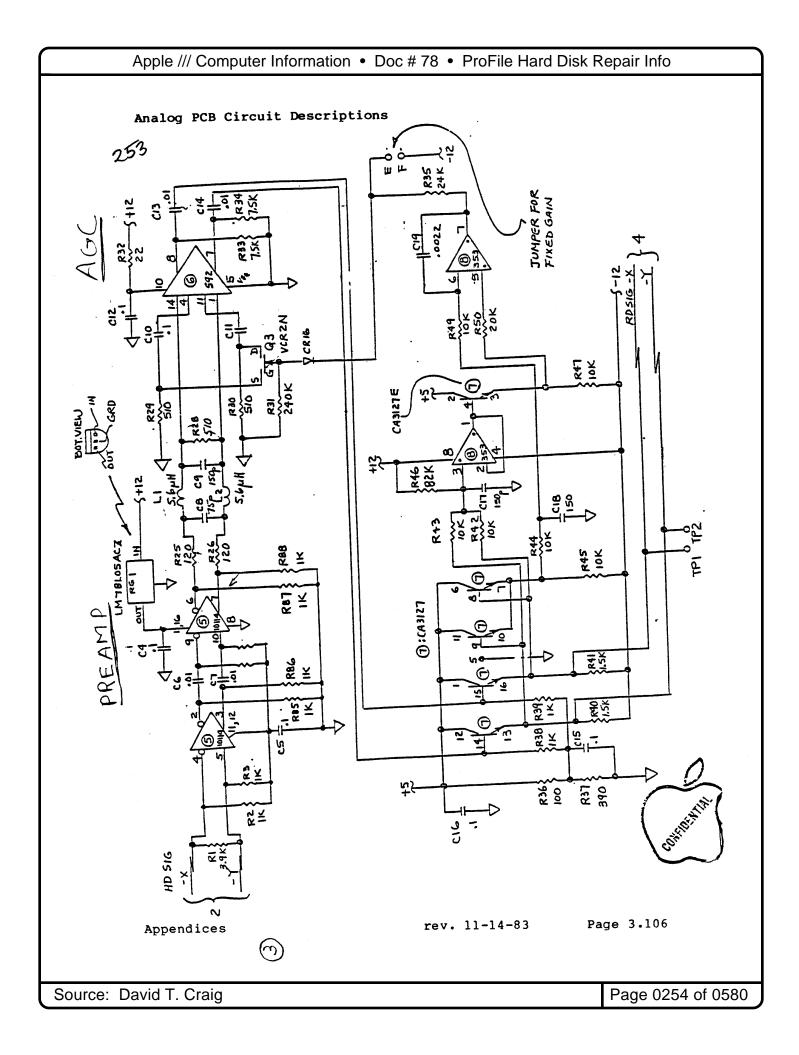

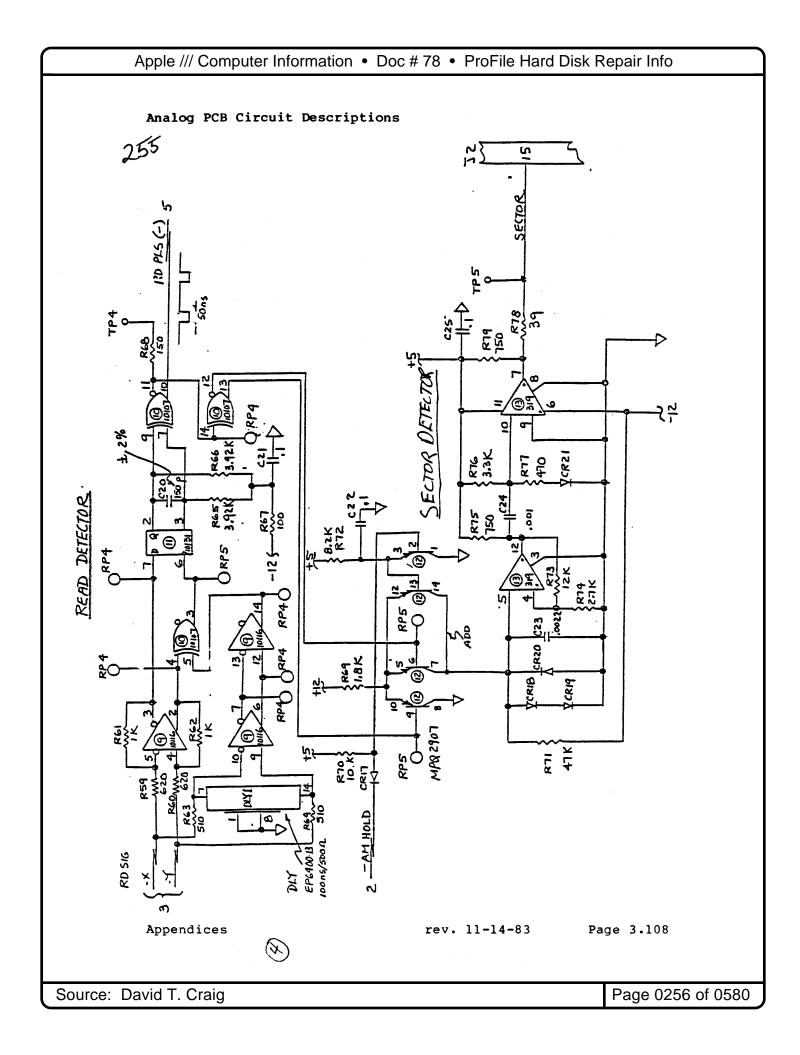

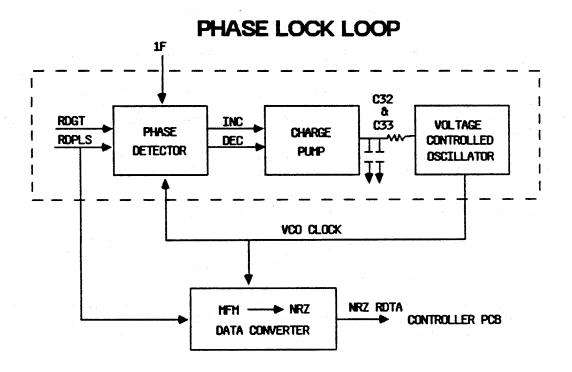

The analog card serves as the interface between the controller and the Head Disk Assembly (HDA). It consists of a data encoder, a data decoder, write driver, head select logic, automatic gain control (AGC) preamplifier, read detector, phase lock loop (PLL), and sector detector.

The head select matrix selects one of the four heads for a read or write operation. The ProFile has two fixed disks in its HDA, and there are two heads for each disk (one for each side, since the disks are double sided). Thus you have a choice of four heads, depending on which section of the disk you are trying to access. It is not necessary for you to know which section of the disk you are trying to access; the controller

2-8

Source: David T. Craig Page 0006 of 0580

and the analog board take care of that for you.

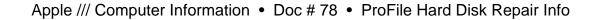

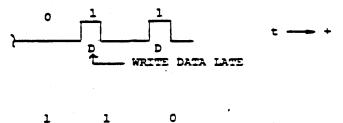

During a write operation, the serial data is encoded using a technique known as MFM. It is not important that you know what this is, just that it allows the maximum data storage with low formatting overhead. In otherwords, it lets you get a lot of data in a small amount of space.

During a read operation, the AGC circuit amplifies the low level head signal (.6 to 2.0 mv) to a fixed signal level (1.0 volt). The read detector simply shapes the signal so that it appears in a standard fashion. The PLL and data decoder then convert this signal back into serial data, which is passed to the controller, which in turn converts it to parallel data and passes it to the Apple ///.

When the disk is initially formatted, the sector boundaries are written to the disk (this is done by removing all read signals from certain sections of the media). During the read operation, the sector detector looks for these areas of no read signal, and signals the controller that a sector boundary has been found.

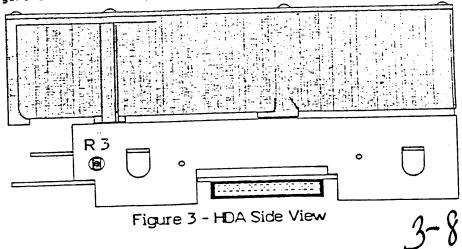

#### Head Disk Assembly (HDA)

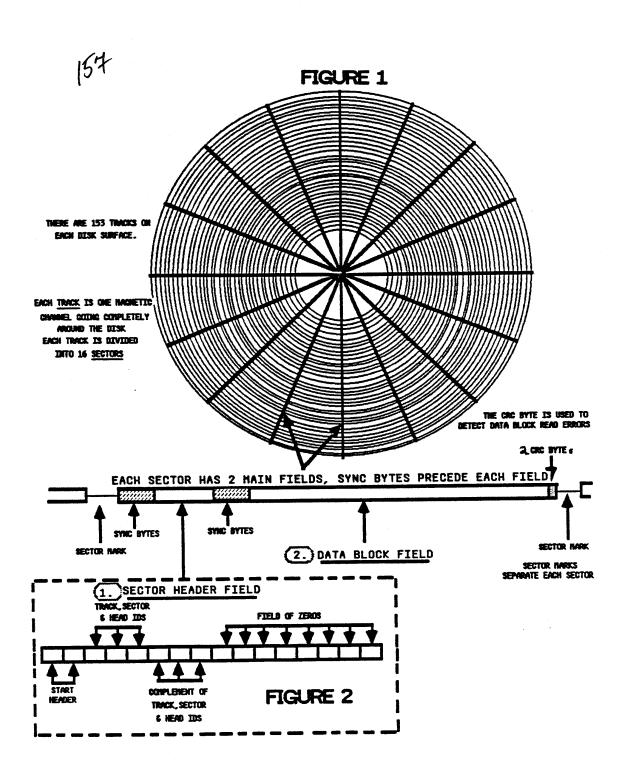

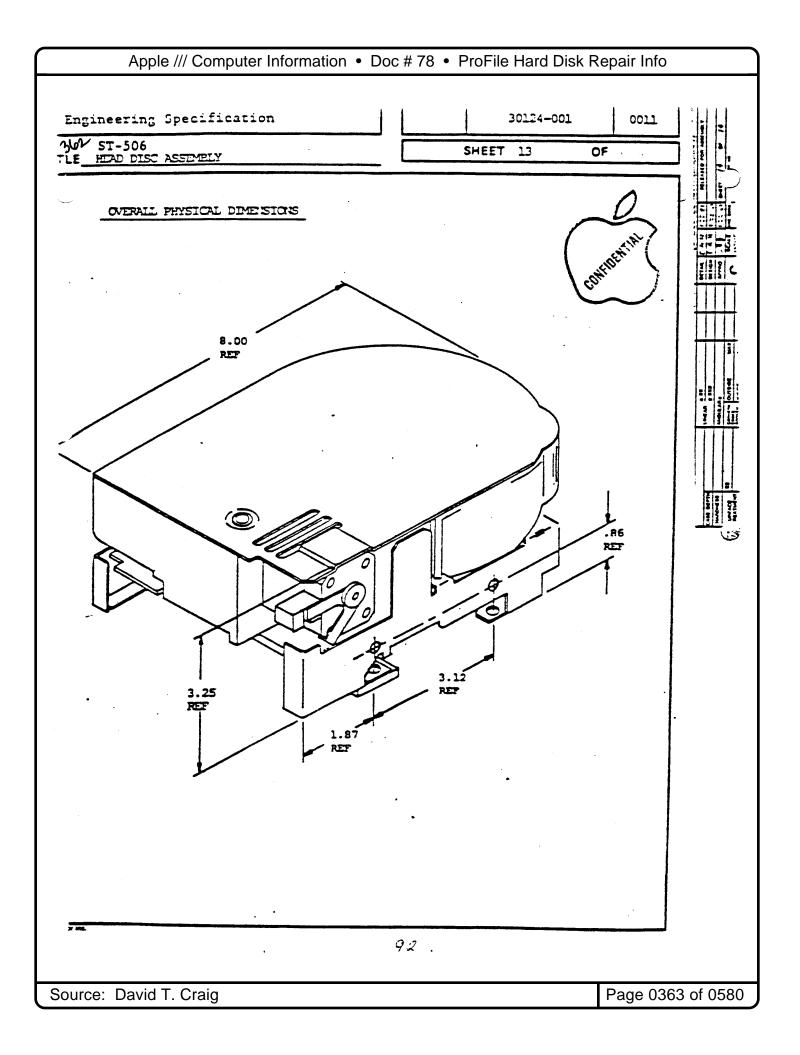

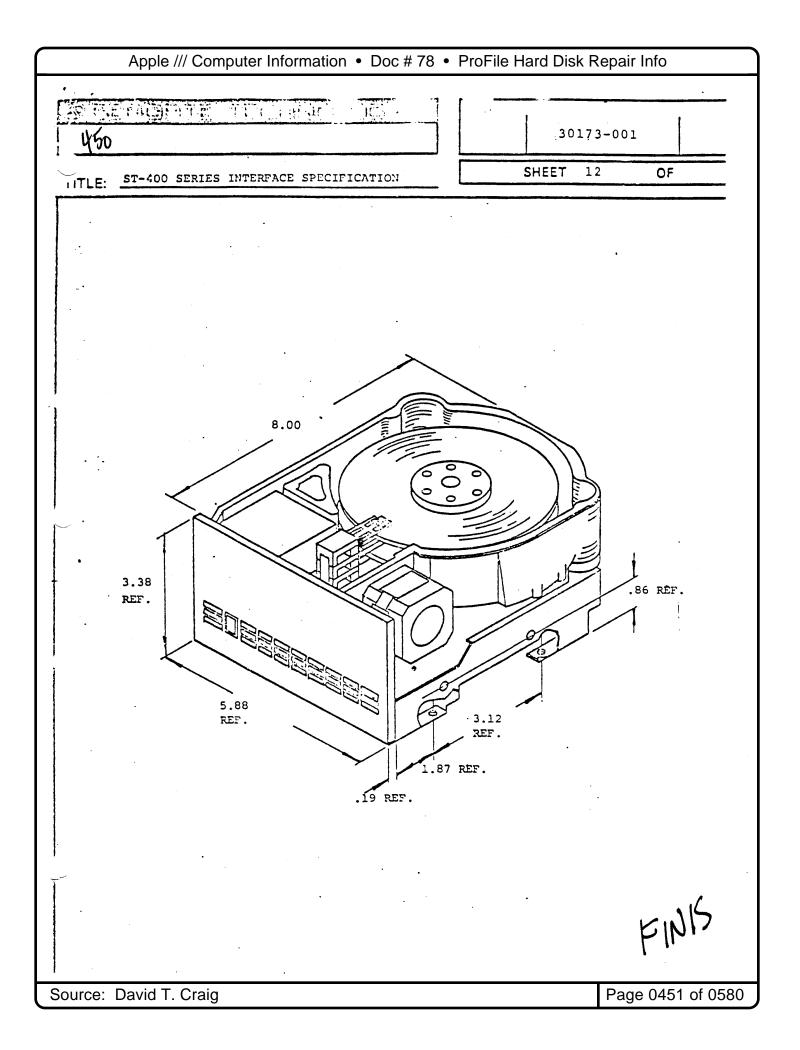

The ProFile HDA is a random access storage device with two non-removable 5 1/4 inch discs as storage media. Each disk surface employs one movable head to service 153 data tracks. The total formatted capacity of the four heads and surfaces is 5 Megabytes (16 sectors per track, 532 bytes per sector, 612 tracks).

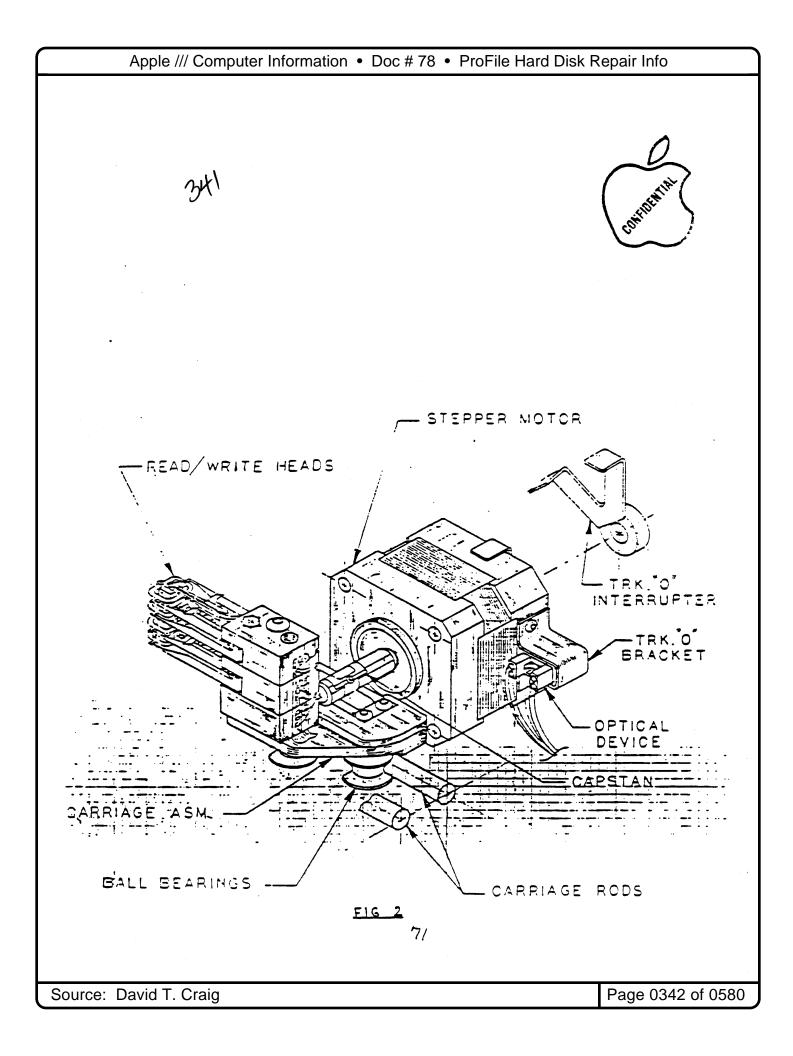

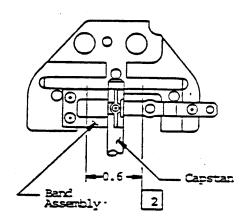

High reliability is achieved through the use of a band actuator and open loop stepper head positioning mechanism. The read/write heads are mounted on a ball bearing supported carriage which is positioned by the band actuator connected to the stepper motor shaft. The inherent simplicity of the mechanical design and electronic control allows maintenance free operation for the life of the drive (designed for over 10,000 hours MTBF). All PCB's are mounted outside the HDA for easy serviceability.

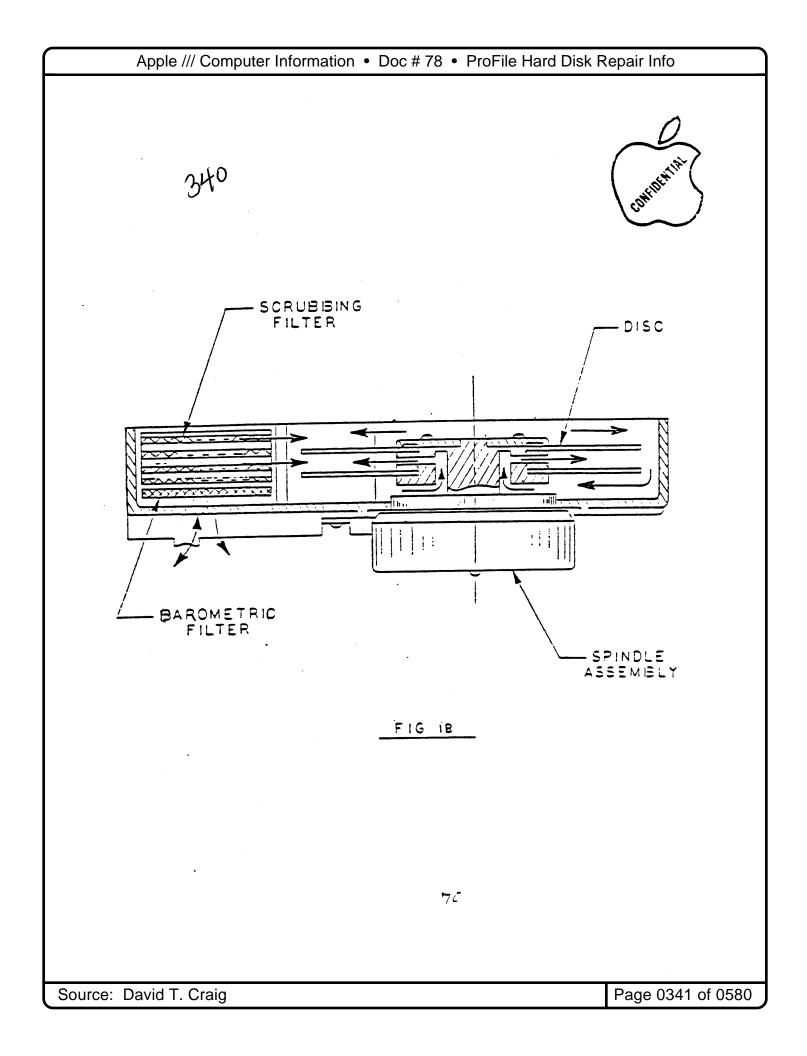

Mechanical and contamination protection for the heads, actuator, and discs are provided by an impact resistant aluminum enclosure. A self contained recirculating system supplies clean air through a 0.3 micron filter. a special spindle pump assures adequate air flow and uniform temperature distribution throughout the head and disk area. Thermal isolation of the stepper and spindle motor assemblies from the disc enclosure provides significantly greater "off track" margin (temperature changes are less likely to cause read errors). Additionally, read and write operations can be performed immediately after power on without waiting for thermal stabilization.

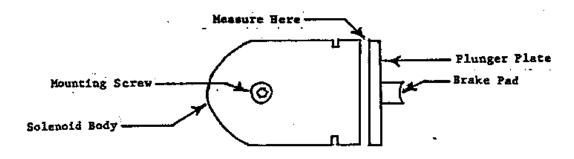

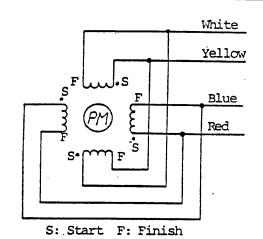

A brushless DC drive motor rotates the spindle at 3600 RPM. The spindle is driven directly with no belt or pulley. The motor and spindle are dynamically balanced to insure a low vibration level. A brake is used to provide a fast stop to the spindle motor when power is removed.

3-8

Source: David T. Craig Page 0007 of 0580

#### Apple /// Computer Information • Doc # 78 • ProFile Hard Disk Repair Info

7

The recording media consists of a lubricated thin magnetic oxide coating on a 130 mm diameter aluminum substrate. This coating formulation, together with the low load force, low mass Winchester type "flying heads", permits reliable contact start/stop operation.

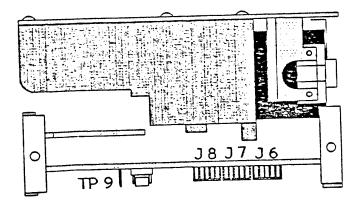

#### Interface Card

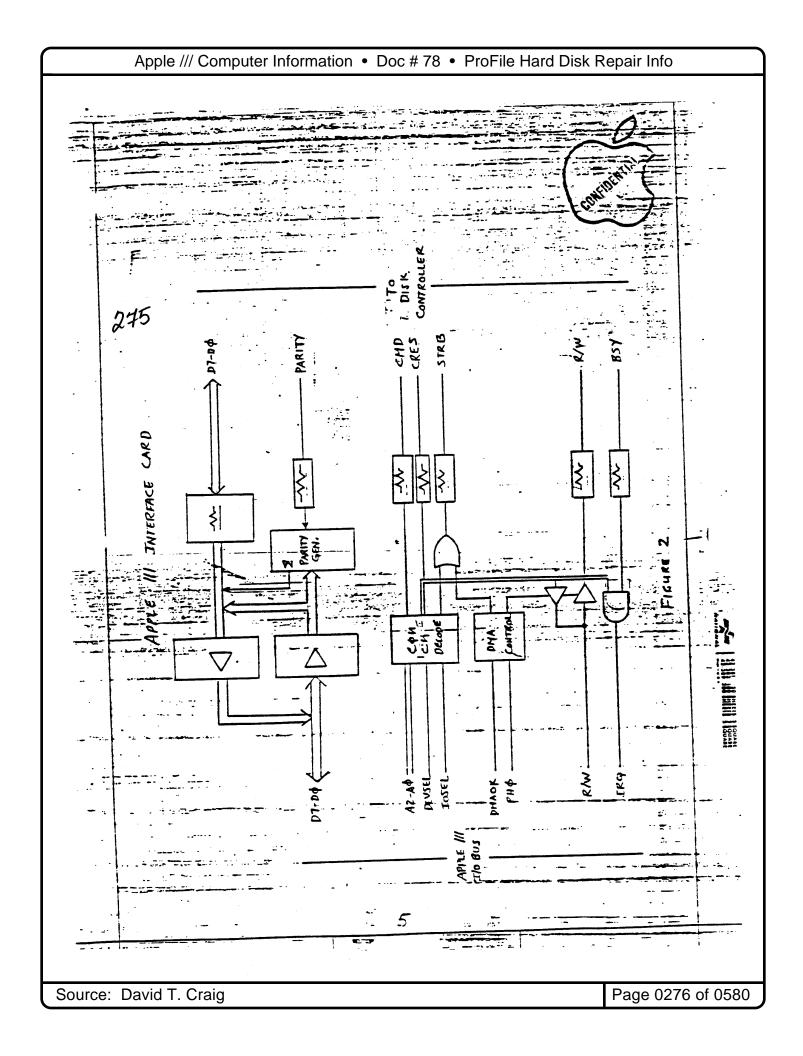

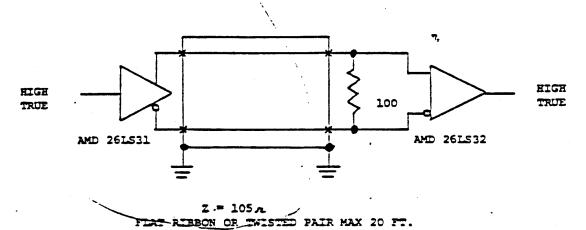

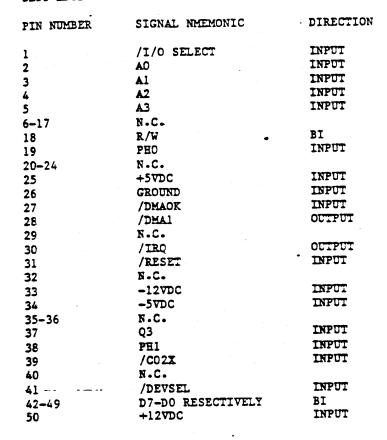

The Apple /// interface card serves primarily to buffer the data and decoded control lines of the Apple /// for transmission to the ProFile controller card. The interface card may be plugged into any of the four Apple /// expansion slots. Eight bi-directional data lines and five control lines are connected to the ProFile controller card with a 25-conductor cable. Each signal is buffered by an RC network fo EMI/RFI suppression. Bytes may be transferred either one at a time or by DMA at 1 Megabyte per second.

4-8

Source: David T. Craig Page 0008 of 0580

Apple III

#### ProFile - The Reliability Story

With thousands of ProFiles already installed, we have been asked to explain what Apple has done to make the ProFile so reliable. This is how we do it:

Design Simplicity:

Experience shows that the fewer parts there are, the less that can go wrong. Profile was designed to work in harmony with the personal computer, resulting in fewer electronic and mechanical parts than any comparable Winchester design. There are fewer things that can go wrong with Profile.

ProFile is designed to prevent problems:

Throughout the design process, the question was asked: "What can go wrong?" The answers were taken into account as the design proceeded. For instance, ProFile moves the heads to a "parking position" off the data zone after three seconds of no activity. This prevents the loss of data if, for instance, the ProFile is dropped or jarred. ProFile constantly checks for errors during operation. After any change in tracks, ProFile verifies that the operation has been performed correctly. ProFile also checks that the heads are positioned accurately on a track before any read or write operation is performed. Unless the system requests that the ProFile do otherwise, data is always verified after a write operation. In all these cases, ProFile will correct the problem so that no errors occur.

Many types of systems are prone to failures when the power is turned on or off. The ProFile power supply is designed to sense a power failure well before the internal DC voltages drop. This allows the intelligent controller in ProFile to prevent any data loss if the power fails or is turned off accidentally. The system will not begin any operation until the power is on for at least one second.

Superior System Margins:

For the user, a system with greater operating margins results in superior reliability. Profile will operate correctly and handle data correctly under adverse environmental and mechanical conditions. For example, the packaging of Profile enables it to withstand a one inch (2.5 cm) drop while operating, or a three inch (7.6 cm) angled drop while not operating. The HDA (head disk assembly) can be operated from  $10^{\circ}\text{C}$  to  $60^{\circ}\text{C}$ . This wide operating range, combined with a 75% efficient switching power supply allows Profile to operate from  $10^{\circ}\text{C}$  in still air without a fan!

High speed, low noise ECL (emitter coupled logic) provides wide margins for the analog electronics section of ProFile. Motor speed is kept accurate within 4%. Automatic gain control combined with a unique "gated detector" can compensate for off track operation up to 20%. Data can be read correctly with up to 50% signal degradation.

5-8

Source: David T. Craig

ProFile can Detect and Even Correct Problems:

The intelligent controller which is built into ProFile is continually checking the operation of the disk. In addition to the "problem prevention" functions already described, ProFile performs additional operations to assure that the user will never see a problem. These operations start the moment ProFile is turned on. After power-up, ProFile does a scan of the entire disk surface, and checks for any errors. Upon any data error, an extensive analysis of the error is performed to determine whether a media error exists. If that is the case, the data will be moved to a spare sector of the disk. That part of the disk with a media error will no longer be used. In most cases, the data recovery routines in ProFile will be able to extract the data even from a bad sector. The recovery operation includes more than 300 retries under various conditions. Maps of the bad sectors are redundantly recorded on ProFile so that an error in the map will not cause a problem in operation.

ProFile is Designed for Performance:

Data can be transferred from the ProFile to the system at up to one Mbyte per second DMA rate. Data is interleaved at a 5:1 ratio, which allows three 512 byte sectors to be transferred on each rotation. MFM encoding allows the maximum data storage capacity with low formatting overhead.

Profile has been Exhaustively Tested in Design and Manufacturing.

During product development, over 200,000 hours of testing were logged. Over forty systems were customer tested for three months before volume production began. Each ProFile is tested for 184 hours prior to shipment, 60 of which are at  $60^{\circ}$ C. This commitment to quality ensures a 10,000 hour MTBF with typical performance of over 24000 hours MTBF. ProFile is truly the most reliable product of its type.

#### PROFILE:

#### APPLE'S 5 MEGABYTE PERSONAL MASS STORAGE SYSTEM for the APPLE ///

#### FEATURES:

#### 1. ProFile has 5 Megabytes of storage capacity

- 2. Less than 44 cents per 1000 bytes

- 3. ProFile accesses data 10 times faster than the conventional floppy disk drive.

- 4. ProFile's intelligent controller automatically scans for error conditions and relocates marginal data blocks elsewhere on the disk, if necessary.

- 5. ProFile has a flexible backup scheme using the Backup /// Utility.

- 6. ProFile is fully supported by Apple ///s Sophisticated Operating System.

- 7. Many different application programs can be stored on ProFile. Using Catalyst software from Quark Engineering, various software programs stored on ProFile, can be selected and then loaded from the hard disk without re-booting floppy diskettes when you want to go from one program to another.

- 8. Profile is compact, lightweight, 8. Profile is usable in any work styled like the Apple /// and Monitor ///, simple to install, and extremely quiet.

#### BENEFITS:

- 1. Simplifies large data processing and programming tasks.

- 2. Provides cost-effective data storage.

- 3. Increases productivity.

- 4. Assures data integrity.

- 5. Assures data security.

- 6. Apple /// software utilizes ProFile without requiring any changes. Different types of programs can often use the same data base.

- 7. Saves time normally lost when booting up numerous floppies. Reduces media wear because programs are booted directly from the ProFile.

- environment.

7-8

Source: David T. Craig Page 0011 of 0580

#### MARKETS AND APPLICATIONS

ProFile is an ideal tool for....

- \* Financial Planners: who can make better decisions, because Profile lets them draw on a greater data base in generating answers to questions about pricing, market share, profits, etc. In addition, all financial modeling files created with programs such as VisiCalc can be stored in one place allowing the planner to switch quickly from one file to another.

- \* <u>Software Developers:</u> Profile lets developers keep all successive versions of programs on the same disk, thus making development time less tedious and time-consuming.

- \* <u>Graphics Designers:</u> Thanks to ProFile's fast access time, plots, charts, and finished graphics can be displayed many times faster than with conventional diskettes. ProFile also makes it possible to create highly sophisticated graphics programs that require large amounts of storage space.

- \* Professionals: ProFile lets doctors, dentists, lawyers, consultants, and other professionals store large client record files all in one place.

- \* Managers in small to medium size businesses: Profile has the storage capacity to hold many letters, memos, reports, and other documents in a single place.

8-8

Source: David T. Craig

2

Apple Computer, Inc. Service Engineering Department

# Apple /// Computer Repair Document

Pro File Hard Disk

DOCUMENT TITLE

ProFile Limited Data Recovery

Author: Apple

DAVID T. CRAIG 736 EDGEWATER, WICHITA, KANSAS 67230 [USA]

Source: David T. Craig Page 0013 of 0580

### rapple computer inc.

6 pages

13

ProFile Technical Procedures

#### Section 1

Apple /// ProFile Limited Data Recovery

#### Contents:

| Introduction1.           | 3 |

|--------------------------|---|

| What You Should Do First |   |

| Software Overview        |   |

| Equipment Required1.     |   |

| Configuring the Software | 4 |

| Setting Up the System    | 4 |

| Running the Program      | 5 |

| Interpreting the Results | 7 |

ProFile Data Recovery rev. 4/20/83

page 1.1

Source: David T. Craig

Page 0014 of 0580

### **K**apple computer inc.

#### ProFile Technical Procedures

Apple /// ProFile Limited Data Recovery and Exchange

#### Contents:

#### Section 1

| Introduction                |

|-----------------------------|

| What You Should Do First1.3 |

| Software Overview1.3        |

| Equipment Required1.4       |

| Configuring the Software    |

| Setting Up the System       |

| Running the Program         |

| Interpreting the Results1.7 |

#### Section 2

| ntroduction                        | .2.3    |

|------------------------------------|---------|

| aterials Required                  | .2.3    |

| emoving the Cover                  | .2.5    |

| emoving the cover                  | . 2. 7  |

| moving the LED Assembly            | 2 7     |

| installing the New LED Assembly    | . 2 . / |

| eplacing the Cover and Rear Plates | . 2.9   |

| ackaging for Shipment              | .2.1    |

| ummary of Procedures               | .2.1    |

| dilliary of flocedares.            |         |

ProFile Technical Procedures rev. 4/20/83

page 0.1

Source: David T. Craig

Page 0015 of 0580

## is apple computer inc.

#### A. INTRODUCTION

This ProFile Limited Data Recovery Program is used with Apple /// ProFiles. It attempts to copy customer's files from a damaged ProFile to the exchange unit. Although there is no guarantee that data can be transferred, in most cases data recovery is possible if the ProFile passes the self test after being turned on.

If the ProFile READY light does not come on to a steady state, data cannot be recovered using this program. Special arrangements must be made with Level 2 for data recovery.

The importance of regular backups should be emphasized to the customer. The customer should have a copy of the Backup /// diskette (part number 681 0032). The documentation for this is "Apple /// Backup User's Manual" (part number 030 0381).

CAUTION: Before continuing with this procedure use the "Apple /// Confidence Program" (part number 681 0031) to ensure that the Apple /// is functioning properly. Failure to do this could possibly damage the ProFile!

#### B. WHAT YOU SHOULD DO FIRST

First run the confidence program and make sure that the Apple /// is functioning properly. Then  $\underline{\text{make a back-up copy of the Recovery Program diskette!}}$  You will be using a system with known bad hardware attached to it, so don't take a chance of destroying the software accidentally. Put the original in a safe place.

#### C. SOFTWARE OVERVIEW

The diskette accompanying this document contains software designed to recover a large portion of data found on a damaged ProFile. In order to use this program the customer's ProFile must complete the power-up cycle, which includes a testing sequence. That is, the red "READY" indicator must be on and steady. If this does not occur, data recovery is not possible.

The program copies data from the customer's ProFile to the exchange unit. If the program has difficulty writing to the Exchange ProFile, it should stop. Something could be wrong with the Exchange unit, so try another Exchange unit. As data is copied, those blocks which the program had problems reading are identified. After the blocks are copied, all further operations are performed on the exchange unit.

ProFile Data Recovery

rev. 4/20/83

page 1.3

Source: David T. Craig Page 0016 of 0580

IΨ

#### apple computer inc.

The program examines each file to see if any of its blocks were among those which couldn't be copied. A printed record indicates the files that couldn't be copied as being suspect and, most probably, unusable. While this is going on, the master allocation map for the entire ProFile is also being rebuilt. The allocation map tells which blocks are used and which are free for use.

Our testing has shown that of the ProFiles that become "READY", the program is able to recover most all of the customer's data.

#### D. EQUIPMENT REQUIRED

Recovery Program Diskette

Apple /// System (256k)

Monitor

Compatible Printer

Printer Interface Card (if not using the Silentype printer)

ProFile Interface Card (2 required)

ProFile Interface Cable (2 required)

#### E. CONFIGURING THE SOFTWARE

The Recovery Program software is configured for two ProFile drivers and the Silentype printer. If you use the Silentype printer no configuration is necessary. If you wish to use a printer which uses the built-in serial port or an interface card, use the System Configuration Program to add the appropriate driver. (Refer to the Standard Device Drivers Manual.) Delete the .PRINTER driver already configured. Whatever printer driver you use must be named .PRINTER as the program looks for this name for its output.

Do <u>not</u> under any circumstances, make any changes to either of the two ProFile drivers. These are named **.GOOD** and **.BAD**, and  $\underline{\text{must}}$  remain that way for the program to run correctly.

When you have the software properly configured, make another copy and use it as your working diskette. There is really no point in taking the chance of destroying the one you just configured.

ProFile Data Recovery

rev. 4/20/83

page 1.4

Source: David T. Craig

#### i? **Lapple computer inc.**

#### F. SEITING UP THE SYSTEM

- 1. Turn the power off on the Apple /// and remove the cover.

- 2. If necessary, install an interface card for the printer in the slot for which you configured its driver.

- 3. Configure the Apple /// with two ProFiles as follows: Install the ProFile interface cards in slots three (3) and four (4). These are the two right-most slots as you look at the Apple from the keyboard side. Seat the cards firmly in the slots.

- 4. The ProFile Electronic Module contains two circular markers, one red and one green. Place the <u>red</u> marker on the cable connected to the ProFile card in <u>slot 4</u>. Place the <u>green</u> marker on the cable connected to the card in <u>slot 3</u>. (Addition markers are included in the software package.)

NOTE: You can leave this set-up and whenever you want to use the data recovery procedures all that is necessary it to connect the ProFiles (see next section).

5. Connect the printer and monitor.

#### G. RUNNING THE PROGRAM

NOTE: Before you running the Limited Data Recovery Program, attach the LED to the Exchange ProFile. (See Section 2 for directions.)

- 1. Turn on the monitor.

- 2. Turn on the printer and make sure it is on-line.

- 3. Connect the (good) Exchange ProFile to the cable marked with the green marker.

- 4. Connect the customer's ProFile to the cable marked with the <u>red</u>

CAUTION: Check that the cables are connected correctly or you will copy files from the Exchange ProFile to the customer's, eliminating any chance of saving any files.

5. Connect the power cables to both ProFiles and turn them on.

ProFile Data Recovery

rev. 4/20/83

page 1.5

#### apple computer inc.

- Wait until the "READY" lights on both ProFiles show steady red.

This will take a minute or so.

- Place the Recovery Program Diskette in the Apple /// built-in drive.

- 8. Turn on the Apple /// and the program will start.

- 9. When the program starts you will see the message:

Watch the ready light on the EXCHANGE ProFile. Please press the RETURN key when you're ready.

When you press RETURN, the READY light on the Exchange ProFile should flash once, indicating that the cables are connected correctly.

If the light does <u>not</u> flash, you may have connected the cables <u>incorrectly</u>. Press the ESCAPE key (to prevent the recovery <u>process</u>), check the cables and try again.

10. As a final check, you will see the following displayed:

Are you sure you want to overwrite PROFILE? (PROFILE is the name of the Exchange ProFile.)

Enter "Y" if the ready light flashed, or ESCAPE if the ready light did not flash:

Answer yes by entering a Y to begin the recovery process.

- 11. An asterisk (\*) in the upper right hand corner of the screen will blink to indicate that the recovery operation is working correctly. During the operation, different messages will appear on the screen to let you know what is happening within the program. The operation can take anywhere from 15 to 30 minutes, depending upon how much data can be recovered.

- 12. As sections of the program are completed, messages will be listed to the printer.

- 13. When the program is done, the Apple bell will beep about every five seconds. Press the ESCAPE key to stop the bell and the program.

- 14. Power down both ProFiles. The exchange unit goes to the customer, and the other unit goes to Level 2.

- 15. Turn the equipment off, remove the program diskette and put it away.

ProFile Data Recovery

rev. 4/20/83

page 1.6

Source: David T. Craig

## apple computer inc.

#### H. INTERPRETING THE RESULTS

Give your customer the printed results of the data recovery procedures and a copy of how to interpret these results. In the following explanation, examples of the printout are shown in bold face printing. These statements are interpreted as follows:

#### Apple /// Limited Disk Recovery Program

Results:

Trouble accessing

### All accessible directories are listed below. Individual files which contain problem blocks are also listed.

The resolution of the individual files on the ProFile is shown as a running status, displaying the directory names as they appear on the ProFile. If a file contains one or more "suspect" blocks, its name will appear.

These files are not deleted as they may, in fact, still be partially usable. An example of this would be as ASCII file, such as one created by AppleWriter. An attempt should be made by the customer to access these files. If the attempt results in "unusual" things happening, then delete them.

#### Block Conflict Report

This message appears if two or more files claim use of the same block .Another pass through the ProFile directories is made to resolve it. Along with this message the directory names are listed on the print-out. Those files which conflict with each other will be listed. An attempt is made to repair the problem. If the conflict is resolved, no further mention is made of the files, otherwise the following message appears: Unable to repair all block conflict errors. Try your files.

#### Summary of Allocation Map Changes

This summarizes the changes made to the master allocation map. This will include the total number of blocks available on the ProFile (blocks on volume), the number of blocks in use (blocks used), and the number still available (blocks available).

#### Block(s) released from allocation map

A statement will also appear regarding the number of blocks, if any, released from the allocation map. If blocks were released, the original allocation map "thought" that more blocks were in use than really were. The ProFile returned to your customer contains the updated, correct allocation map.

(The End)

ProFile Data Recovery

rev. 4/20/83

page 1.7

Source: David T. Craig Page 0020 of 0580

3

Apple Computer, Inc. Service Engineering Department

# Apple /// Computer Repair Document

Profile Hard Disk

DOCUMENT TITLE

ProFile Exchange Procedures

Author: Apple

DAVID T. CRAIG 736 EDGEWATER, WICHITA, KANSAS 67230 [USA]

Source: David T. Craig Page 0021 of 0580

#### 21 **Latapple computer inc.**

## Il pages

#### ProFile Technical Procedures

#### Section 2

#### ProFile Exchange Procedures

#### Contents:

| Introduction                        | 2.3   |

|-------------------------------------|-------|

| Materials Required                  | 2.3   |

| Removing the Cover                  | 2.5   |

| Removing the LED Assembly           | 2.7   |

| Installing the New LED Assembly     | 2.7   |

| Replacing the Cover and Rear Plates | 2.9   |

| Packaging for Shipment              | 2.11  |

| Summary of Procedures               | .2.13 |

ProFile Exchange rev. 4/20/83 page 2.1

Source: David T. Craig Page 0022 of 0580

#### apple computer inc.

#### A. INTRODUCTION

When a customer returns a ProFile for servicing, the unit will be exchanged for a spares kit ProFile. Before you exchange the customer's ProFile, run the Limited Data Recovery program (described in Section 1) if there is data the customer wishes to try to recover. Exchanging the ProFile consists of removing the cover, the L.E.D. Cable Assembly and rear plates from the customer's ProFile, then replacing the LED assembly and placing the rear plates and the customer's cover on the Service Spares Kit (Exchange ProFile) unit.

The shipping cover marked "SHIPPING FIXTURE" is attached to the ProFile to be serviced and the entire unit is placed in the same packaging as was the spares kit, and sent back for servicing.

#### B. MATERIALS REQUIRED

Diagonal cutters ("dikes") Tie Wraps Medium Phillips Screwdriver Protective Pad Small Flatblade Screwdriver

CAUTION: The ProFile is a mechanical device with motors and moving parts. Rough handling such as dropping the drive, sharply jarring it or allowing heavy objects to fall on it can cause a malfunction. Whenever it is necessary to turn the ProFile over, be sure to rest it on a protective pad.

ProFile Exchange

rev. 4/20/83

page 2.3

Source: David T. Craig Page 0024 of 0580

## apple computer inc.

#### C. REMOVING THE COVER

- Make sure the customer's ProFile is turned off. Disconnect the power cord and interface cable (ribbon cable) from the back of the ProFile.

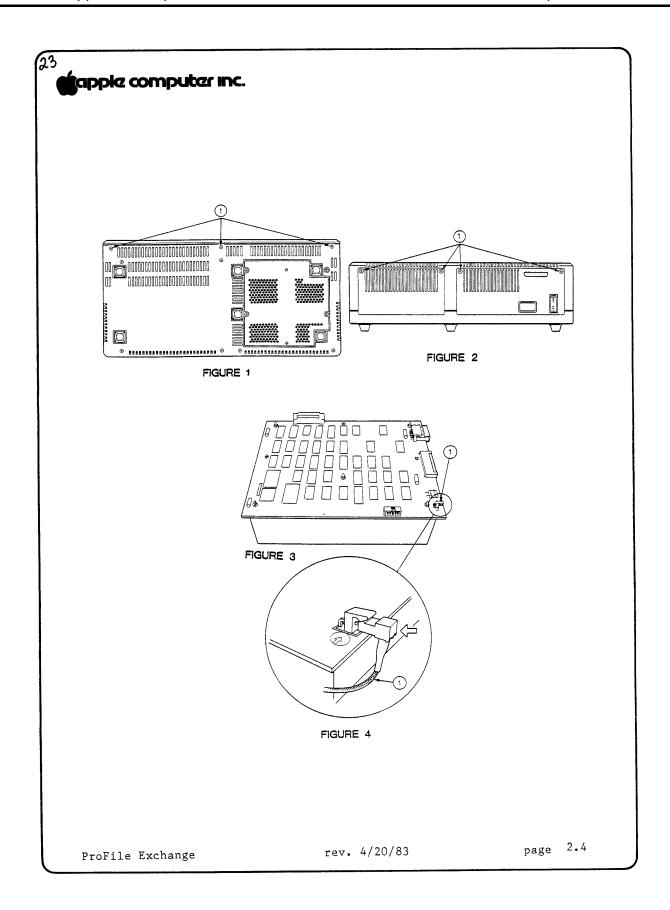

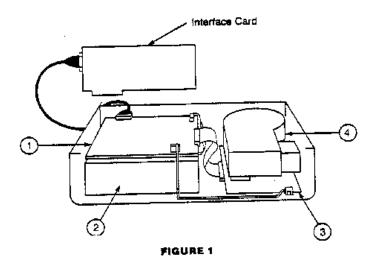

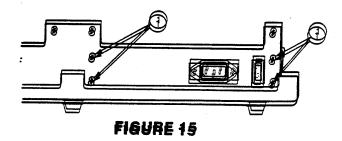

- 2. Turn the ProFile over, lay it on the protective pad, and remove the three Phillips-head screws from beneath the front panel (Figure 1, #1).

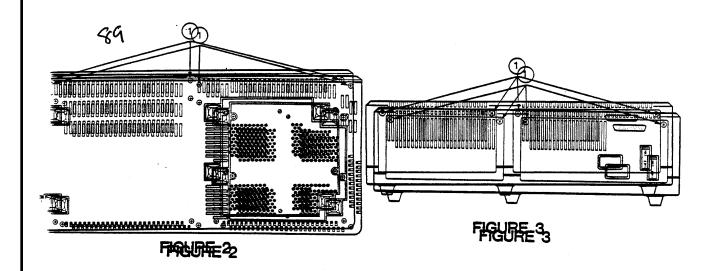

- 3. Turn the ProFile right side up; loosen and remove the four screws on the back of the unit and the two rear plates (Figure 2, #1).

- 4. Lift the cover off carefully and rest it on the far side of the case, taking care not to pull on the LED cable.

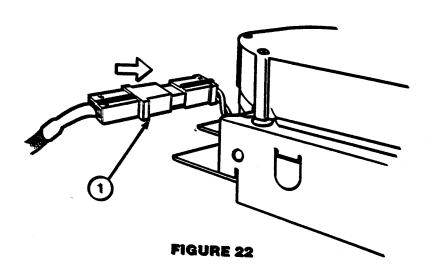

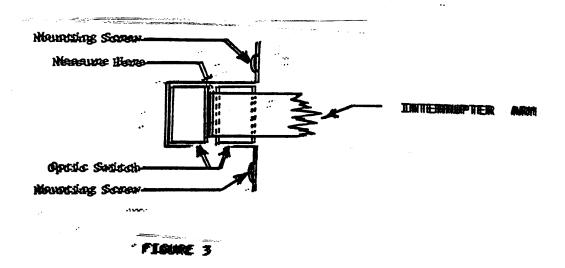

- 5. Unplug the LED cable from its socket on the controller board (Figure 3, #1).

- Remove the cover marked "SHIPPING FIXTURE" from the Service Spare parts module. Note the LED assembly is not attached.

ProFile Exchange rev. 4/20/83 page 2.5

Source: David T. Craig Page 0025 of 0580

Source: David T. Craig Page 0026 of 0580

24/ Capple computer inc.

#### D. REMOVING THE LED ASSEMBLY

- The ProFile cover is removed and the LED cable is disconnected from the controller card.

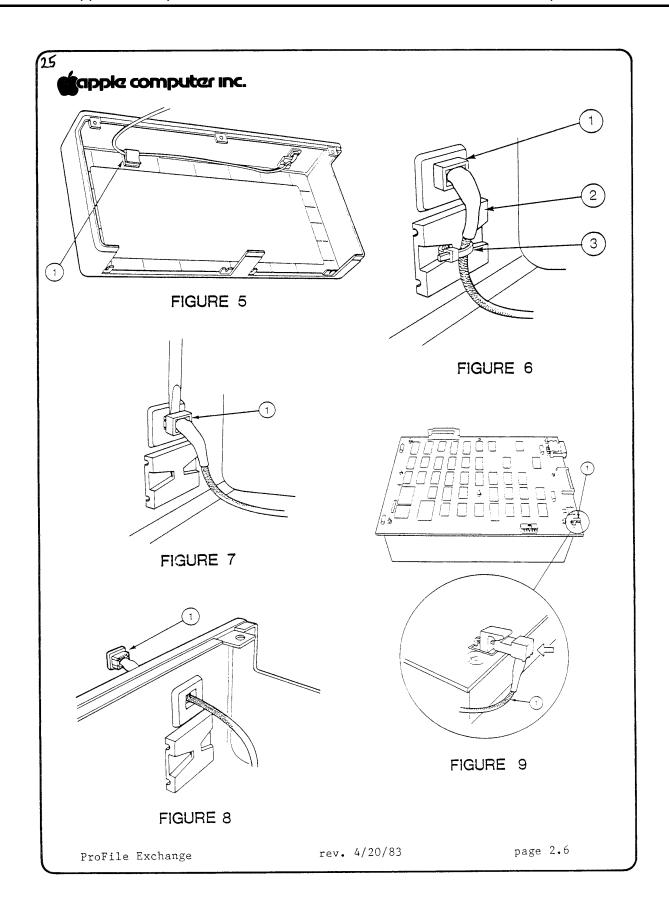

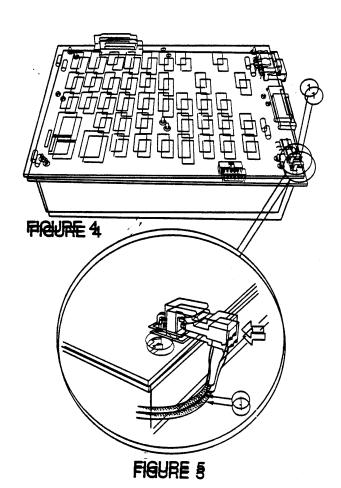

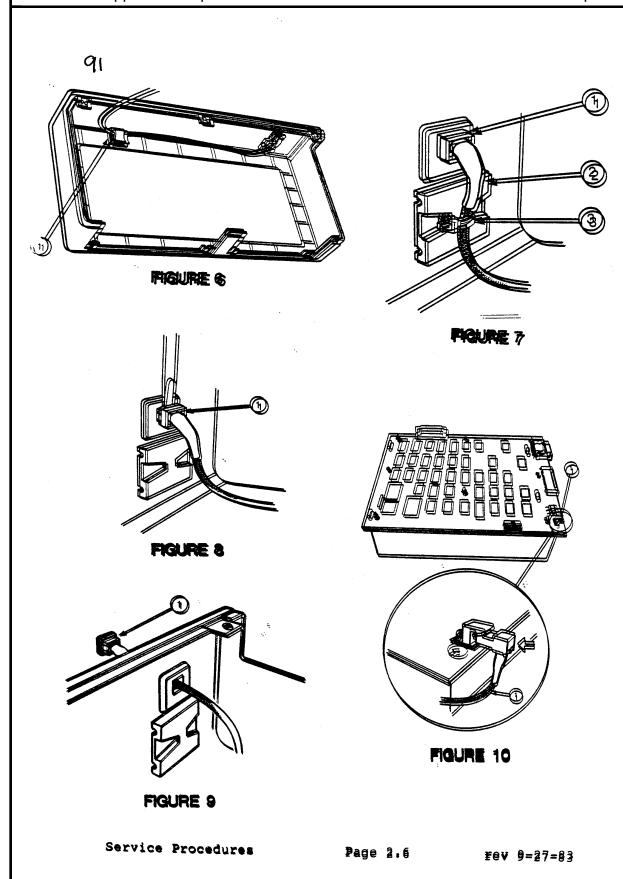

- 2. With the customer's cover laying flat, as in Figure 5, cut off the white plastic tie (Figure 6, #3) that holds the LED cable to the white holder in the cover (Figure 6, #2).

- 3. Remove the other end of the LED cable from the other holder in the cover. (On some ProFiles, this holder will be a clamp like the one shown in Figure 5, #1; on others, it will be like the one shown in Figure 6.)

- 4. With a flathead screwdriver, pry the cable clamp off the back of the LED (Figure 7, #1) and slide it down the cable, out of the way.

- 5. Firmly push a few inches of the cable out through the slot in the cover (behind the "Ready" label) as shown in Figure 8. You will have to remove the "Ready" label around the LED opening on the cover to free the LED.

- 6. Around the red LED is a small black plastic mount. Remove the mount (Figure 8, #1) by pushing out its side flaps and sliding it off the LED.

- 7. Pull the cable back through the hole in the case.

#### E. INSTALLING THE NEW LED ASSEMBLY

- 8. Take the LED from the Service Spares Kit and thread it through the front opening in the cover. Place the small black plastic mount on the LED (see Figure 8, #1), then pull the cable back through the opening until the LED fits in its slot. Replace the "ready" label with the new label found in the spares kit..

- Push the cable clamp (Figure 6, #1) up to the cover until it holds the cable steady.

- 10. Place the LED cable against the white plastic holder and fasten it with a tie wrap, contained in the spares kit, (Figure 6, #2 and 3). Cut off excess tie wrap.

- 11. Place the cable in the other holder (Figure 5, #1), using a tie wrap if necessary. Cut off excess tie wrap.

- 12. Connect LED cable to controller card (Figure 9). Place Customer's LED Cable Assembly and old "Ready" label in the bag, from which you got the new assembly, to be returned with the ProFile to be serviced. Put the customer's cover on the Spares Kit ProFile.

ProFile Exchange

rev. 4/20/83

page 2.7

Source: David T. Craig

Source: David T. Craig Page 0028 of 0580

#### **Éapple computer inc.**

#### F. REPLACING THE COVER AND REAR PLATES

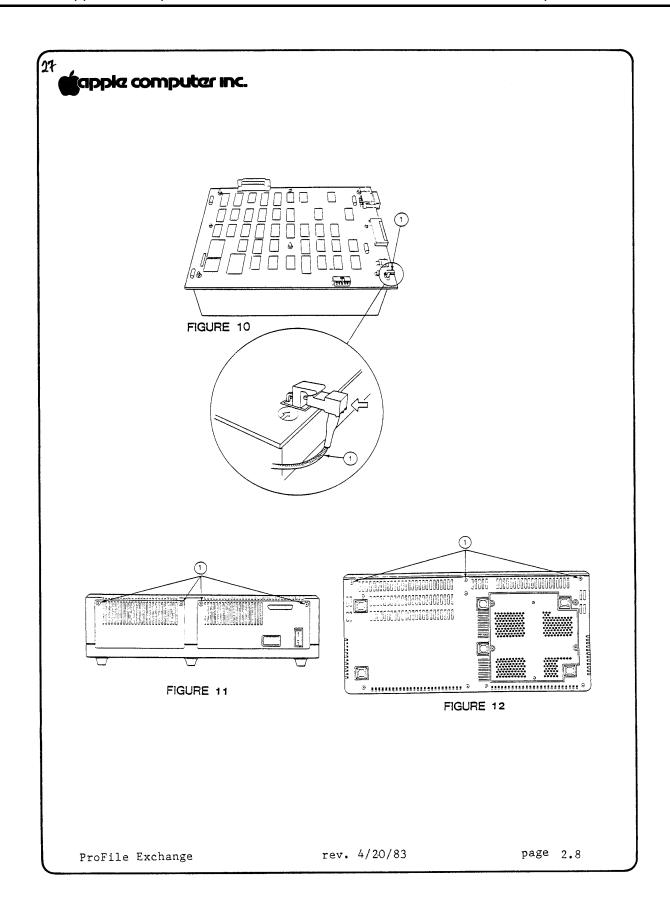

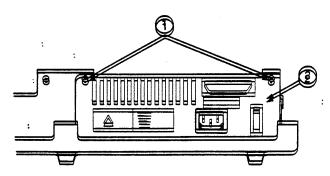

- 1. Attach the LED cable to its connector on the controller card (Figure 10). Make sure the LED cable exits down and away from the card (Figure 10, #1).

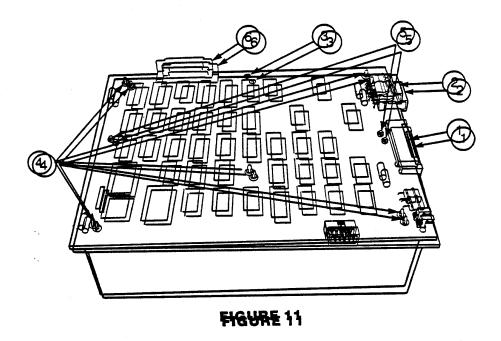

- 2. Replace the two rear plates and the four screws. Do not tighten the screws at this time (Figure 11).

NOTE: The serial number is stamped on one of the rear plates and must be transferred to the ProFile which the customer will keep.

- 3. Replace the customer's ProFile cover on to the spares module. (Hint: The four slots on the back of the cover fit between the inner and outer rear plates. Line up the back first; then pull the cover gently forward and down. Check around the cover to make sure the LED cable isn't caught between the cover and the base.)

- 4. Tighten the four rear-plate screws.

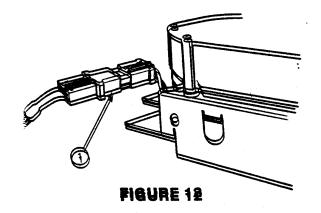

- 5. Turn the ProFile over and replace the three screws on the front edge (Figure 12).

- Turn the ProFile right side up. Reinstall the power cord and the interface cable.

NOTE: Before replacing the cover on the unit to be serviced, lay the used LED Cable Assembly from the customer's ProFile on top.

7. Replace the cover marked "SHIPPING FIXTURE" on the unit to be returned for servicing.

ProFile Exchange

rev. 4/20/83

page 2.9

Source: David T. Craig Page 0030 of 0580

30 **Mapple computer inc.**

#### G. PACKAGING FOR SHIPMENT

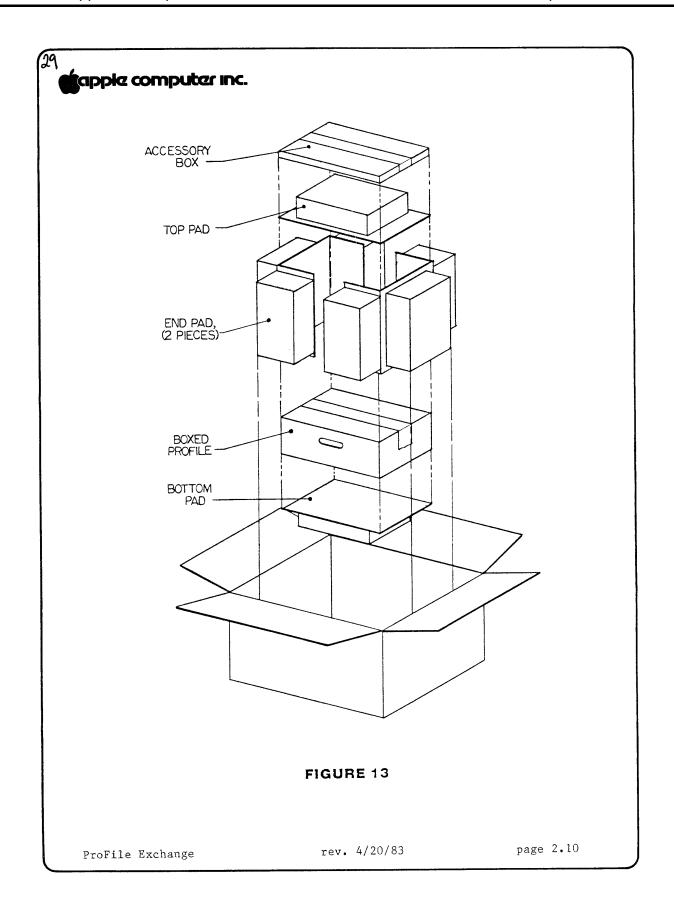

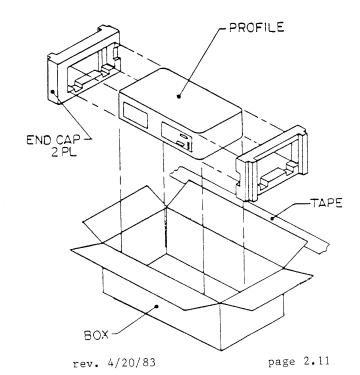

The following instructions refer to Figure 13 unless otherwise stated.

- 1. Set Packing Box on the floor with all flaps facing outside the box.

- Bend the two End Pads and slide them into the box with the foam against the sides of the box.

- Slide Bottom Pad, with the foam side toward the bottom of the box, into position between the end pads.

- 4. Place End Caps snuggly onto the ends of the ProFile (Figure 14).

- 5. Place the boxed ProFile on top of the Bottom Pad.

- 6. Lay the Top Pad with the foam padding facing away from the ProFile, on top of the ProFile.

- Place the Accessory Box, which contains the used LED Assembly, on top of the ProFile.

- 8. Close the end (short) flaps; then the side flaps.

- 9. Secure the flaps using shipping tape.

- 10. Secure shipping documentation to the top of the box.

FIGURE 14

ProFile Exchange

Source: David T. Craig Page 0031 of 0580

| н. | SUMM | ARY OF PROCEDURES CHECKLIST                                                                                                                                                                       |

|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      | Remove the spares kit from its packaging. Keep the shipping materials to package the unit to be sent in for servicing.                                                                            |

|    |      | Remove cover marked "SHIPPING FIXTURE" from the spares kit and verify that all modules are present, all connections are proper, and that there are no loose or broken wires or foreign materials. |

|    |      | Turn on monitor.                                                                                                                                                                                  |

|    |      | Turn on printer and make sure it is on-line. (The driver is already configured for the Silentype printer.)                                                                                        |

|    |      | Connect LED on Exchange ProFile.                                                                                                                                                                  |

|    |      | Connect Exchange Profile (use slot 3 for the Interface card).                                                                                                                                     |

|    |      | Connect customer's ProFile (use slot 4 for the Interface card).                                                                                                                                   |

|    |      | Turn on Apple /// and run the Limited Data Recovery program.                                                                                                                                      |

|    |      | Power down and disconnect both ProFiles.                                                                                                                                                          |

|    |      | Remove both rear plates from the customer's ProFile.                                                                                                                                              |

|    |      | Remove the cover from the customer's ProFile.                                                                                                                                                     |

|    |      | Remove and replace the LED assembly on the cover of the customer' ProFile, using the new LED front panel label.                                                                                   |

|    |      | Attach the two rear plates from the customer's ProFile onto the Exchange (spares kit) ProFile). Note that the serial number is one of these plates.                                               |

|    |      | Replace the customer's cover onto the Exchange ProFile fitting it into place over the two rear plates.                                                                                            |

|    |      | Place the used LED assembly along with the old front panel label in the assembly $\ensuremath{box}\xspace.$                                                                                       |

|    |      | Attach the cover marked "SHIPPING FIXTURE" onto the unit to be serviced.                                                                                                                          |

|    |      | Pack the unit to be repaired and the box containing the used LED assembly in the spares kit packaging.                                                                                            |

|    |      | Complete all shipping documentation.                                                                                                                                                              |

Source: David T. Craig Page 0032 of 0580

# Apple /// Computer Repair Document

Profile Hard Disk

Pro-File Level II. Phase 1 Service

Manual (Preliminary)

Author: Apple

DAVID T. CRAIG 736 EDGEWATER, WICHITA, KANSAS 67230 [USA]

Source: David T. Craig Page 0033 of 0580

Pages: 138

## PRO-FILE LEVEL II PHASE 1 SERVICE MANUAL

**PRELIMINARY**

Source: David T. Craig

Page 0034 of 0580

## PROFILE EQUIPMENT LIST

| 1  | DEBUGGER:                        |

|----|----------------------------------|

|    | FIRMWARE889-9007                 |

|    | 28338-8603                       |

|    | 330-8003                         |

| 2) | SOFTWARE DUPLICATION:            |

|    | FST                              |

|    | QUICK DEBUG (Ver. 7)889-0004     |

|    | FORMAT CERTIFY                   |

|    | BIG DEBUG (Ver. 17)(INCLUDED)    |

|    |                                  |

| 3) | UPGRADE KIT:                     |

|    | MASKED Z8 MICROPROSSOR           |

|    | 6.36 x 5/16 STANDOFF860-0213     |

|    | 5.1K OHM RESISTER101-4512        |

|    | 0.1 MICROFARAD CAPACITOR130-0007 |

|    | 1K OHM RESISTER                  |

|    | 330 OHM DIP PACKS112-0105        |

|    | 3.9K OHM RESISTER                |

|    | 26 TO 30 GAUGE INSULATED WIREN/A |

|    | WINE THOUSAND WINE               |

| 4) | MISCELLANEOUS TOOLS:             |

|    | TEST LED                         |

|    | (CUT DOWN)                       |

|    | JUMPER                           |

|    | (USED DURING FORMAT)             |

|    | ALLEN (hex) DRIVERS              |

|    | (BRAKE ADJUSTMENT 5/64)          |

|    | (TRACK ADJUSTMENT .050)          |

Source: David T. Craig Page 0035 of 0580

### PRO-FILE PHASE 1 SERVICE MANUAL TABLE OF CONTENTS

| Manual Introduction                                                                                                           | i                         |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Section 1 Troubleshooting                                                                                                     |                           |

| Section 1 Introduction                                                                                                        | 1.4                       |

| Section 2 Service Procedures                                                                                                  |                           |

| How To Use This Section                                                                                                       | 2.1                       |

| Pro-File Module Removal/Replacement Procedures                                                                                |                           |

| Introduction  1. The Cover  2. The Ready LED  3. Controller PCB  4. Power Supply  5. HDA and Analog PCB  6. Motor Control PCB | 2.5<br>2.7<br>2.9<br>2.1] |

| PCB Upgrades Controller PCB Upgrade                                                                                           | :.19<br>:.21              |

| Checks and Adjustments  HDA Speed                                                                                             | .24                       |

| Software Operation Procedures  Format Program                                                                                 | .36                       |

Pro-File Phase 1 Service Manual Table of Contents rev 11-28-83

Source: David T. Craig

## PRO-FILE PHASE 1 SERVICE MANUAL TABLE OF CONTENTS

## Section 3 Appendices

| How to Use This Section                                                                      | ••••••                                  | 3.2     |

|----------------------------------------------------------------------------------------------|-----------------------------------------|---------|

| Overview of the Pro-File                                                                     |                                         |         |

| General Information                                                                          |                                         | 2 =     |

| Z. Allatou PCB                                                                               |                                         |         |

| <ol> <li>Switcher Power Supply</li> <li>Hard Disk Assembly (HDA)</li> </ol>                  |                                         | 2 7     |

|                                                                                              | •••••••                                 | 3.8     |

| Pro-File HDA Description                                                                     |                                         |         |

| <ol> <li>Physical Description</li> <li>Pro-File HDA Format</li> </ol>                        |                                         | 2 11    |

| 3. Special Function Tracks                                                                   | ••••••                                  | 3.17    |

| Firmware Routines                                                                            |                                         |         |

| 1. Scan Operation                                                                            | • • • • • • • • • • • • • • • • • • • • | 3.20    |

| 2. Retry (Error/Data Recovery) 3. Diagnostic (Sector Media Check) 4. Normal Operation (Diss. |                                         | 2 22    |

| 4. Normal Operation (Differences fi                                                          | rom Scan)                               | 3.25    |

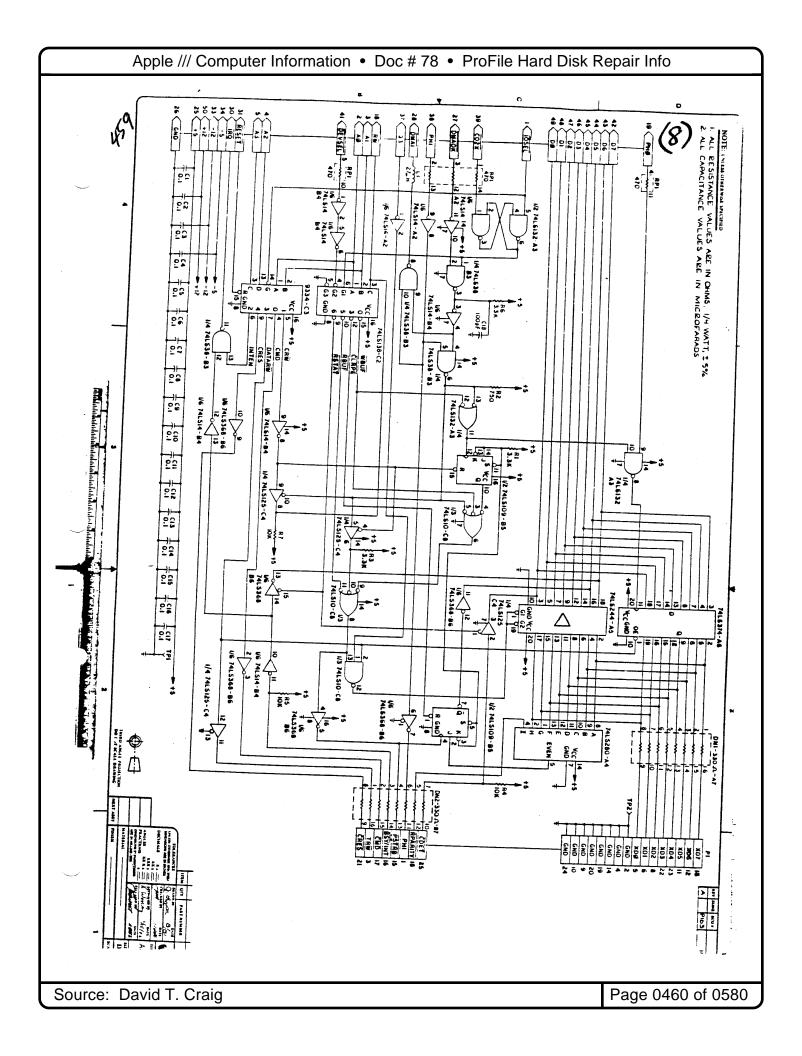

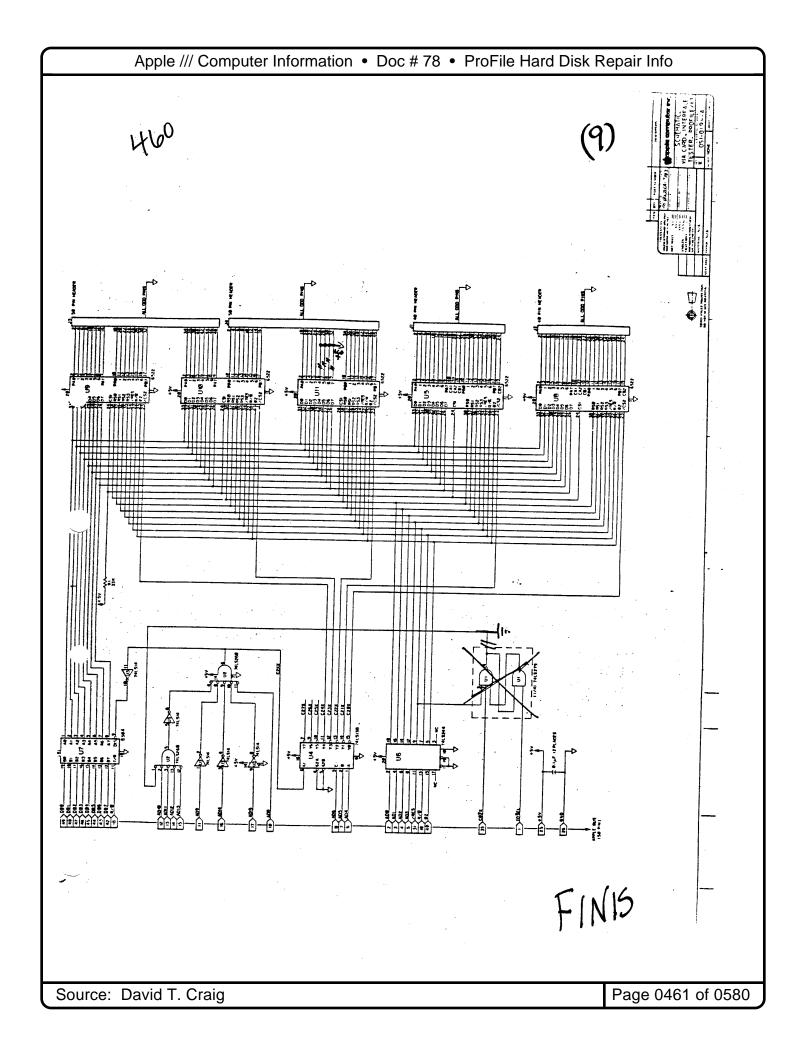

| Circuit Descriptions                                                                         |                                         | 3.20    |

| 1. Controller PCB                                                                            | • • • • • • • • • • • • • • • • • • • • | 2 27    |

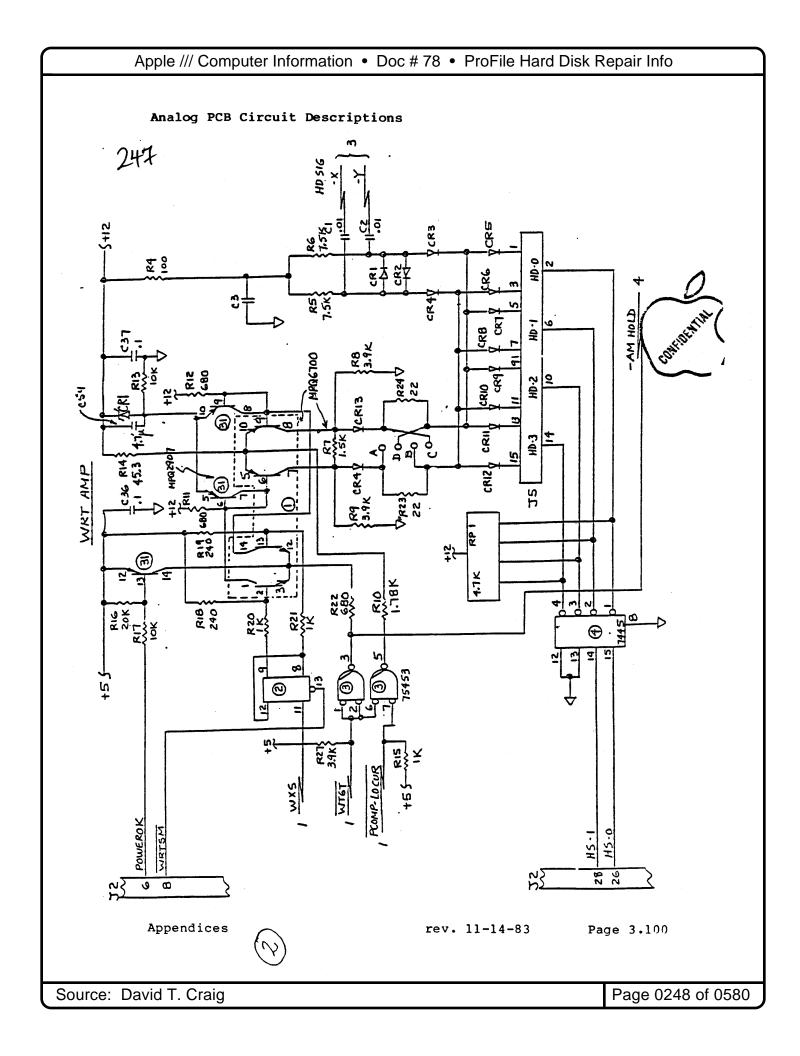

| 2. Analog PCB                                                                                | • • • • • • • • • • • • • • • • • • • • | 3.92    |

| Schematic Diagrams                                                                           |                                         |         |

| 1. Controller PCB                                                                            | • • • • • • • • • • • • • • • • • • •   | 3.124   |

| 2. Analog PCB                                                                                | • • • • • • • • • • • • • • • • • • • • | 2 1 2 5 |

Pro-File Phase 1 Service Manual Table of Contents rev 11-28-83

Source: David T. Craig Page 0037 of 0580

## HOW TO USE THIS MANUAL

The Pro-File Phase 1 Service Manual is divided into 3 sections:

## SECTION 1 TROUBLESHOOTING:

This section contains a flowchart procedure and corresponding explanation for troubleshooting a problem Pro-File to the faulty module.

## SECTION 2 SERVICE PROCEDURES:

This section contains the various procedures needed to test, adjust, and remove or replace the modules on the Pro-File.

#### SECTION 3 APPENDICES:

This section contains various descriptions referred to by the other sections for the purpose of providing general and specific information on Pro-File operation.

Service Manual Introduction Page i rev 9-21-83

Source: David T. Craig Page 0038 of 0580

## Apple /// Computer Information • Doc # 78 • ProFile Hard Disk Repair Info

# 39 SECTION 1 TABLE OF CONTENTS

| Section 1 Introduction 1             | • 3 |

|--------------------------------------|-----|

| Main Troubleshooting Flowchart 1.    | . 4 |

| No Scan Troubleshooting Flowchart 1. | 14  |

| Diagnostic Procedure Flowchart       | 1 2 |

Pro-File Phase 1 Service Manual Page 1.1 rev 9-21-83

Source: David T. Craig Page 0040 of 0580

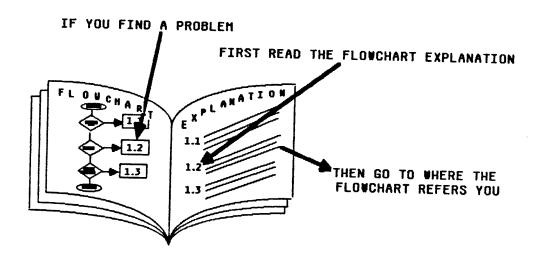

## IMPORTANT READ THIS

#### HOW TO USE THIS SECTION

The procedure in this Troubleshooting Section is concerned with isolating a problem in the Pro-File to a malfunctioning module (i.e. Controller PCB, Analog PCB, Hard Disk Assembly (HDA), or Power Supply).

CAUTION: The Hard Disk Assembly (HDA) is a very expensive and fragile device, handle it gently to avoid damage.

To troubleshoot the Pro-File use the flowcharts in this section beginning with the main flowchart on the next page.

If you find a problem, go to the opposite page and read the explanation for the check that failed. This explanation will provide you with valuable information on the reasoning behind the flowchart, and will also provide you with references to sections 2 and 3 for needed procedures and additional information. After reading the flowchart explanation, you may if you wish take the action indicated at the NO branch of the total section indicated at the NO branch of

\* If you are not familiar with Pro-File operation you may wish to read the Pro-File HDA description and/or the Pro-File Overview in the Appendices Section.

Pro-File Phase 1 Service Manual Page 1.3 rev 9-21-83

Source: David T. Craig Page 0042 of 0580

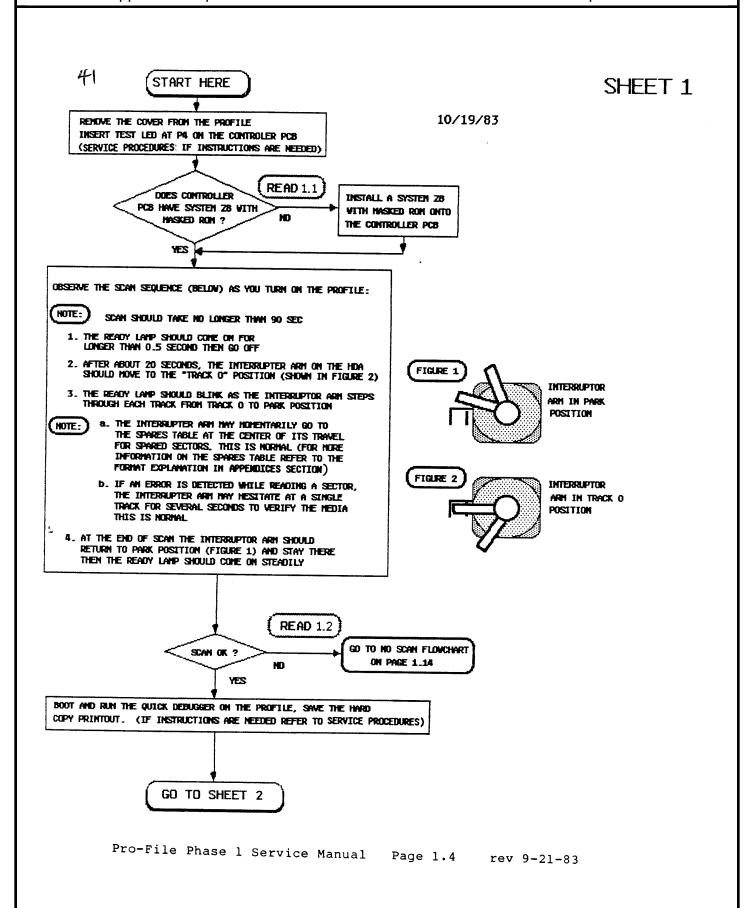

1.1 When the Pro-File first came out the firmware program used for the Z8 microprocessor on the Controller PCB was contained on a ROM chip located piggyback on the Z8. After this version had been out in the field awhile, it was found that due to the heat expansion that occurred when the machine was turned on, the leads from the ROM's piggyback socket were intermittently separating from the Z8.

Since the Z8 would be looking for program instructions when this happened, the temporarily open input would be interpreted as a bit in an instruction code and cause the Z8 to do strange things including putting the Pro-File into Write mode as the heads were doing a seek to a target track. This of course destroyed any sector header and/or data block fields that happened to be passing under the heads as they were on their way to the target track.

Later when a read of the damaged sectors was tried, either as a result of the next power up Scan operation, or a read command from the host computer system, the Z8 would detect the problem and ultimately spare the sector which of course made the malfunction look like a media problem.

The logical solution for the imagined media problem (the 28 problem was not known at the time) was to replace the now badly formatted (though undamaged) HDA with a new HDA. This action would cause the Pro-File to work fine until the piggyback ROM again separated from the 28. The HDA would be replaced again, ... etc.

Needless to say this process was not very effective. The masked ROM Z8 has been developed to be an effective solution to this problem. All piggyback Z8s are to be replaced with this version. It is projected that most of the current Profile problems will be remedied by this upgrade. (Now return to the point in the flowchart which referred you to this discussion.)

All functions performed by the Controller and Analog PCBs and the HDA are ultimately controlled by the firmware program in the 28 microprocessor on the Controller PCB. During power up on the Pro-File the 28 will have the Pro-File go through a Scan operation in which certain specific things are checked for. A detailed explanation of the Scan operation may be found in Section 3 of this manual. (Now proceed to the NoScan flowchart.)

Pro-File Phase 1 Service Manual Page 1.5 rev 9-21-83

Source: David T. Craig Page 0043 of 0580

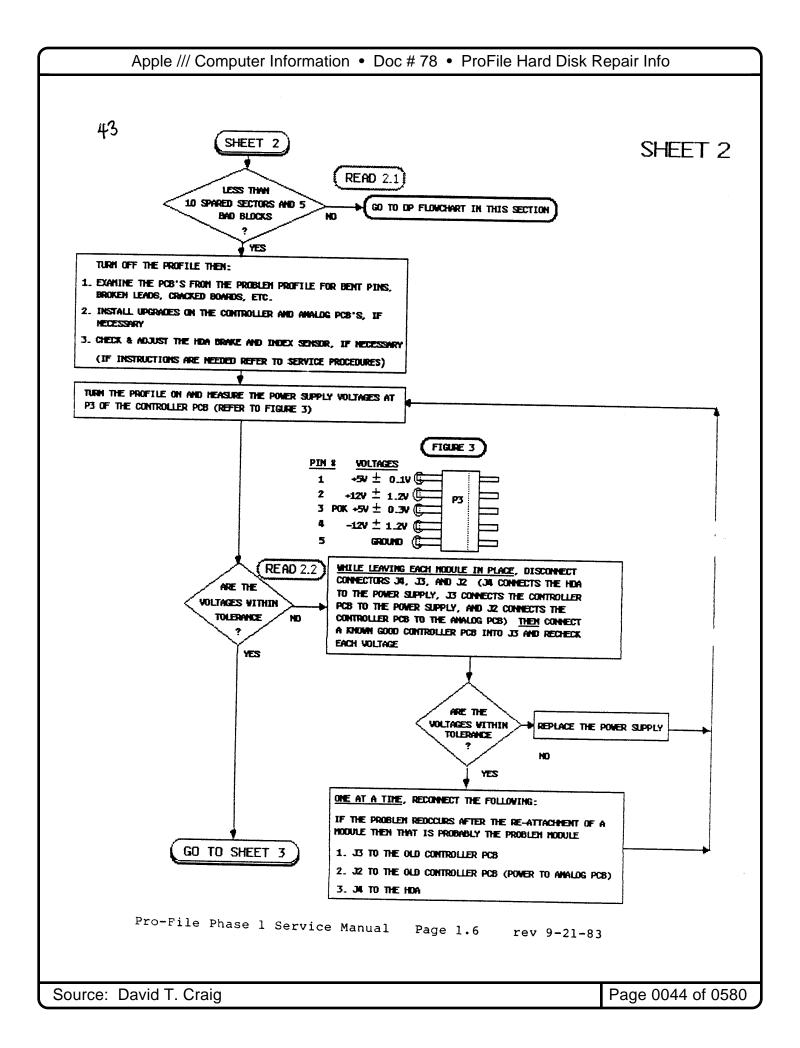

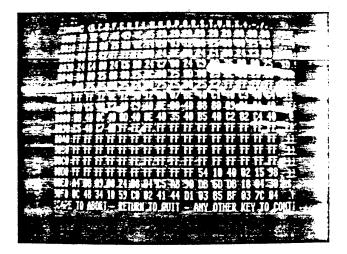

- 2.1 The Quick Debugger program reads the Spares table on the Profile and prints the original sector location of every spared sector listed in that table. Additional information on sparing sectors may be found in the Special Function Tracks explanation in the HDA format description in the Appendices Section of this manual. At this point in the flowchart you know that Scan worked OK, but that the HDA has spared too many sectors. Spared sectors can be caused by either:

- 1. Electronic problems causing a sector to be unreadable or somehow alter its data bit pattern at the original sector location on the disk. For example the 28 may have malfunctioned as it was performing a Seek, and instructed the electronics to write as the heads were moving across the media to a target track. This of course would destroy the parts of all the sectors that the head passed over on its way to the target track.

- 2. Media problems making it impossible to record magnetic information on a sector where it occurs. This could be a manufacturing defect in the media (the magnetic coating on the disk), or a ding in the media caused by head contact.

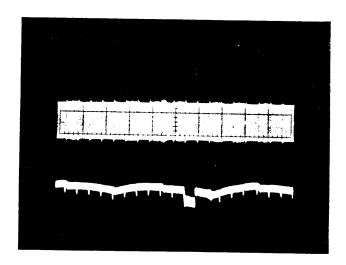

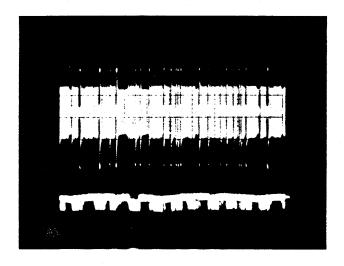

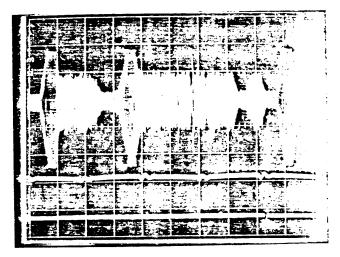

One way to determine whether a spared sector was caused by a media problem or an electronic problem is to continuously read the questionable sector and examine its analog signal with an oscilloscope. The Quick Debugger printout gives you a list of spared sectors that you might want to look at. The DP (Diagnostic Procedure) flowchart that you are being referred to, will explain how you can continuously read a spared sector and interpret its analog signal. (Now proceed to the DP Flowchart.)

2.2 A missing or out of tolerance voltage can be caused by any of the modules in the Pro-File. The method used in this flowchart to isolate the problem module is to disconnect the power supply from all the modules, plug in a known good Controller PCB and monitor the voltages at P3 (the power supply connection to the Controller PCB). If the power supply is at fault then the voltage/s will still be missing or out of tolerance.

WARNING: At least one module must be connected to the Power Supply at all times to provide it with a load.

If the voltages are OK with the known good Controller PCB installed, then the problem must be with a module other than the power supply. To determine which of these modules is causing the power problem, each module is reconnected one at a time and P3 is checked after each reconnection. (Now return to the flowchart.)

Pro-File Phase 1 Service Manual Page 1.7 rev 9-21-83

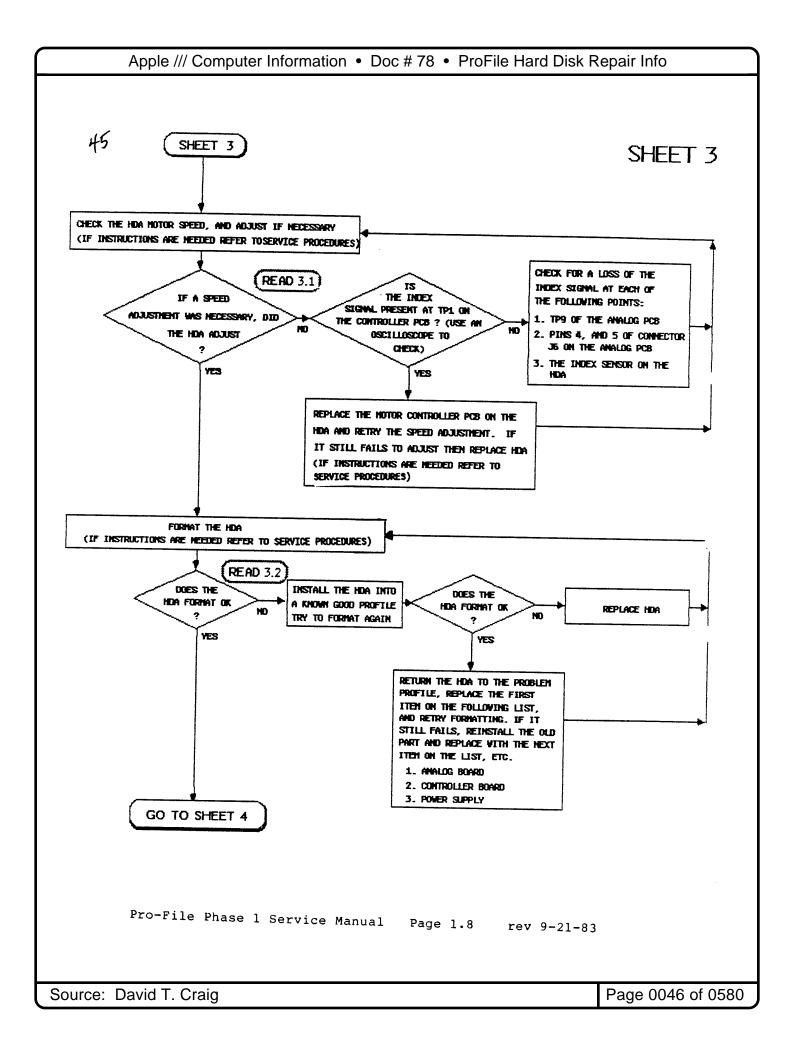

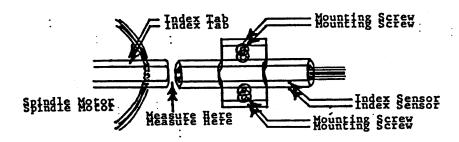

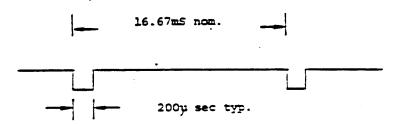

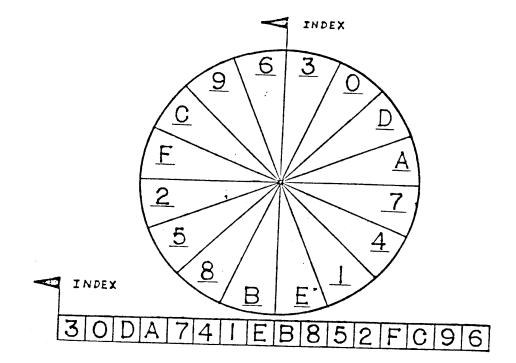

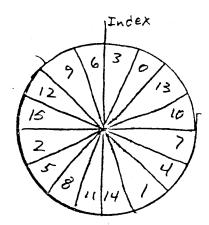

3.1 The Index signal is never actually used by the Pro-File electronics after the HDA has been formatted. During the format process, Index is used to provide a reference for the sectoring scheme to be put on the disk. (For an explanation of the Format used on the Pro-File refer to the Pro-File HDA Description in the Appendices section of this manual.)

But the Index does provide the technician with an indication of actual disk speed. It should occur once per revolution just before sector 0 on disk surface 0. Since the disk speed is supposed to be 3600 RPM this means that the frequency counter should measure a 16.666 ms period between each Index pulse.

If the Index signal is present at TPl of the Controller PCB, but will not adjust as per directions in the Index Check and Adjustment procedure in the Service Procedures Section of this manual, then the problem could be with the electronics on the Motor Controller PCB on the HDA, or with the disk motor on the HDA. If the signal is absent at TPl on the Controller PCB, then flow should be traced back to the Index sensor on the bottom of the HDA. (Now return to the point in the flowchart which referred you to this discussion.)

3.2 During the Format process all sector headers and marks are erased and the spares tracks (track 77 on all disk surfaces) are erased. An inability to format could be caused by an electronic problem in the Pro-File, or by the HDA. If the HDA formats OK after putting it into a known good Pro-File, then the problem is probably with one of the electronics modules in the Pro-File. (Now return to the point in the flowchart which referred you to this discussion.)

Pro-File Phase 1 Service Manual Page 1.9 rev 9-21-83

Source: David T. Craig Page 0047 of 0580

Source: David T. Craig Page 0048 of 0580

4.1) The FST (Final System Test) is an exersizer/tester program used to determine whether or not the Pro-File is operating within acceptable limits.

For approximately the first 10 minutes of the FST, the data block field of every sector is written to and read to detect any CRC read errors.

The system Z8 is used during this test, so the same firmware routines (i.e. Scan, Seek, Read, Retry, Diagnostic, etc.) will be used. After the initial 10 minute write/verify has been performed, the FST exercises the Profile by doing random Seeks, Reads, etc. until its operation is terminated when the operator presses the <ESCAPE> key.

The reason the flowchart has you check for problems after the first 15 minutes of FST is because most hard failures will probably produce errors within 5 minutes after the FST begins to exercise the Pro-File. At this point in the flowchart errors can be caused by 2 types of problems:

1. An Electronic problem which has caused a sector to be unreadable by altering the data bit pattern at its original sector location on the disk. For example the Z8 may malfunction as it performs a Seek, and instruct the electronics to write as the heads move across the media to a target track.

This of course would destroy the parts of all the sectors that the head passes over on its way to the target track (the head should never write during a seek).

2. A Media problem which has made it impossible to record magnetic information on the sector where it occurs. This could be a manufacturing defect in the media (the magnetic coating on the disk), or a ding in the media caused by head contact during rough handling.

The big question at this point is which of the 2 types of problems described above is the real culprit. If the error was caused by an itermittent electronic problem producing a bad format on the HDA, then this looks like an HDA (media) problem. However, if the HDA is replaced the problem will probably reoccur in time. (This discussion is continued on the next page.)

Pro-File Phase 1 Service Manual Page 1.11 rev 9-21-83

4.1 (continued) The method this flowchart uses to determine which type of problem caused the error is to compare the sector locations of sectors that had errors before formatting (a list of these sectors was printed out when you ran the Quick Debugger program on the problem Pro-File), with those produced after formatting (these will be shown by the FST).

If they are the same, then the problem which caused the errors, is probably bad media because bad media locations don't change, so the HDA should be replaced.

If they are different, then the problem is probably electronic. This is because it is highly unlikely that an intermittent electronics problem would occur on the same sector twice.

(If you would like further information on spared sectors, firmware routines, the Pro-File's HDA format, etc., you may refer to the descriptions in the Appendices Section of this manual.)

If the faulty sectors were the same, and the number of errors exceeds those specified by the FST service criteria sheet (found in the Service Procedures Section), then replace the HDA and return to the point in the flowchart which referred you to this discussion.

If they are different, then the problem is probably electronic and you need to look at some of the different faulty sectors to determine what is bad about them and so determine which module is faulty. The DP (Diagnostic Procedure) flowchart that you are being referred to, will explain how you can continuously read a spared sector and interpret its analog signal. (If there were different sectors, then proceed to the DP Flowchart.)

Pro-File Phase 1 Service Manual Page 1.12 rev 9-21-83

Source: David T. Craig Page 0050 of 0580

Apple /// Computer Information • Doc # 78 • ProFile Hard Disk Repair Info 50 THIS PAGE LEFT BLANK INTENTIONALLY Pro-File Phase 1 Service Manual Page 1.13 rev 9-21-83 Source: David T. Craig Page 0051 of 0580

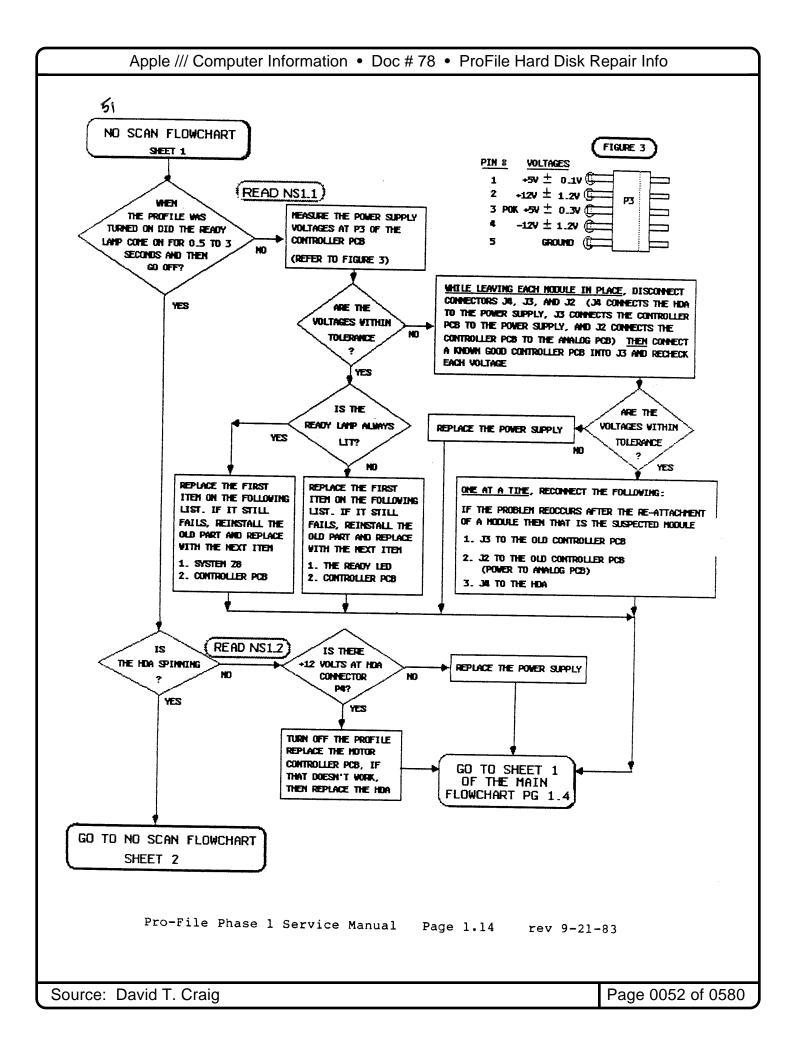

NS1.1 Upon power up on the Pro-File the Z8 will wait for the POK (Power OK) signal to occur. This signal is generated by the power supply when it determines that the proper voltage levels for each voltage have been reached and stabilized. When it happens the Z8 will cause the Ready lamp to extinguish. This should happen within 1/2 to 3 seconds of power up.

A missing or out of tolerance voltage can be caused by any of the modules in the Pro-File. The method used in this flowchart to isolate the problem module is to disconnect the power supply from all the modules, plug in a known good Controller PCB and monitor the voltages at P3 (the power supply connection to the Controller PCB). If the power supply is at fault then the voltage/s will still be missing or out of tolerance.