Cromemco

#

Input/Output Processor

Instruction

Manual

#### IOP OUTPUT PORTS <del>ଅଧ</del>୍ୟ 82h 83h 814 Contraction of the Contract of CANTERIOR TRACTOR ----D7 D7 D7 Not Used Not Used Input Data Empty Input Data Empty D6 D6 D6 Not Used Not Used Output Data Available Output Data Available D-5--D 5 D5 Status 5 Status 5 C-Bus Clear C-Bus Clear D4 D4 D4 04 D4 D4 Status 4 Status 4 C-Bus Available C-Bus Available Used to Transfer Used to Transfer Data From IOP Pata From IOP to Host Processor to Host Processor Used to Furnish Used to Furnish Interrupt Vector interrupt Vector to Host Processor to Host Processor D3---D3 D3 D3-D3 Status 3 Status 3 S-100 Reset S-100 Reset D2 D2 D2 D2 Enable IOP FARMINACIP Interrupts D 2 Status 2 Status 2 D1 D1 - <del>D</del>1 Clear S-100 Clear S-100 Reset Latch D1-Command Register CARRAGAND Register Empty 00 00 D0 Enable S-100 Finehlapi Fleduest Interrupt Request 00 DC Status 0 Status 0

#### 88h 83h 82h 418 nor yetë Output Data Empty Output Data Empty D6 D6 D6 D6 D6 Input Data Available Input Data Available D.5 D.5 D.5 D5 D5 D5 D5 1 (Hard Wired) 1 (Hard Wired) D4 D4 D4 D4 D4 D4 CPU Disconnect CPU Disconnect Meaning Specified Meaning Specified by User's Firmware by User's Firmware or Software Used to Transfer Used to Transfer Data From Host Pata From Host Pata From Host Processor to IOP D3 D3 D3 D3 Interrupt Pending Interrupt Pending D2 D2 D2 D 2 Reset Request Reset Request D1 D1 D1 D1 Status Register Status Register Empty D1 D1 DO DO D0 <del>00</del> 00 Command Available Available

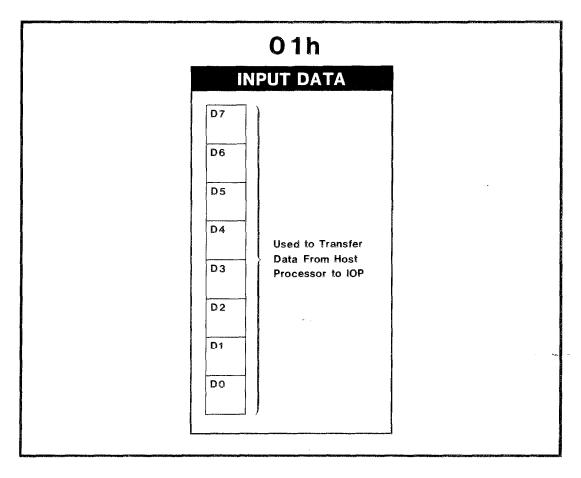

IOP INPUT PORTS

# **Cromemco**®

# Input/Output Processor C-Bus Controller (IOP)

Instruction Manual

CROMEMCO, Inc. 280 Bernardo Avenue Mountain View, CA. 94043

Part No. 023-2006

May 1982

Copyright © 1981,1982 CROMEMCO, Inc. All Rights Reserved This manual was produced on a Cromemco System Three computer utilizing a Cromemco HDD-22 Hard Disk Storage System running under the Cromemco Cromix<sup>TM</sup> Operating System. The text was edited with the Cromemco Cromix Screen Editor. The edited text was proofread using the Cromemco SpellMaster<sup>TM</sup> Program and then formatted using the Cromemco Word Processing System Formatter II. Final camera-ready copy was printed on a Cromemco 3355A printer.

### TABLE OF CONTENTS

### TECHNICAL SPECIFICATIONS

| ABOUT THIS MANUAL                                                                                                                                                                                                                                                                                                                     | 1                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Chapter 1: INTRODUCTION                                                                                                                                                                                                                                                                                                               |                                                         |

| Chapter 2: IOP OPERATING INSTRUCTIONS                                                                                                                                                                                                                                                                                                 | 7                                                       |

| 2.1 IOP Block Diagram 2.2 IOP Central Processing Unit 2.3 IOP RAM Memory 2.4 IOP ROM Memory 2.5 IOP Memory Mapping PROM 2.6 IOP I/O Registers 2.7 IOP Reset and Power On Clear State 2.8 IOP Connectors, Pin Outs and Cables 2.9 IOP/Host Communication 2.10 IOP/C-Bus Peripheral Communication 2.11 IOP Set Up and Initial Check Out | 8<br>10<br>12<br>12<br>16<br>22<br>26<br>29<br>34<br>52 |

| Chapter 3: INTERRUPTS AND DMA                                                                                                                                                                                                                                                                                                         | 57                                                      |

| 3.1 C-Bus Interrupts 3.2 S-100 Bus Interrupts 3.3 Interrupt Programming Examples 3.4 C-Bus DMA 3.5 S-100 Bus DMA                                                                                                                                                                                                                      | 57<br>65<br>69<br>73<br>76                              |

| Chapter 4: IOP THEORY OF OPERATION                                                                                                                                                                                                                                                                                                    | 79                                                      |

| 4.1 IOP Power 4.2 Clocks 4.3 The IOP CPU 4.4 IOP Dynamic RAM 4.5 IOP ROM Memory 4.6 IOP Input/Output Registers 4.7 External C-Bus Memory and I/O Ports 4.8 S-100 Bus Interface 4.9 IOP Interrupt Logic 4.10 C-Bus Interface 4.11 C-Bus Waveforms                                                                                      | 79<br>79<br>79<br>80<br>84<br>84<br>86<br>89<br>90      |

| Appendix A: IOP REG | ISTER DESCRIPTIONS | a | 99  |

|---------------------|--------------------|---|-----|

| IOP Parts List      |                    |   | 115 |

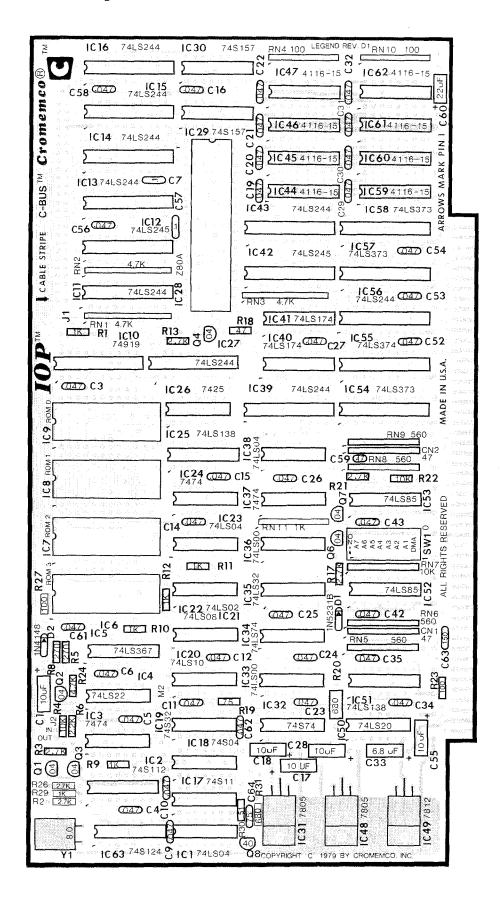

| IOP Parts Location  | n Diagram          |   | 119 |

| IOP Limited Warra   | nty                |   | 121 |

| IOP Schematic Diag  | gram               |   | 122 |

A

## **FIGURES**

| Figure   | 1:  | Cromemco's C-Bus Architecture               |              |

|----------|-----|---------------------------------------------|--------------|

| Figure   | 2:  |                                             | 4<br>9<br>13 |

| Figure   |     |                                             | د ا          |

| Figure   |     |                                             | 15           |

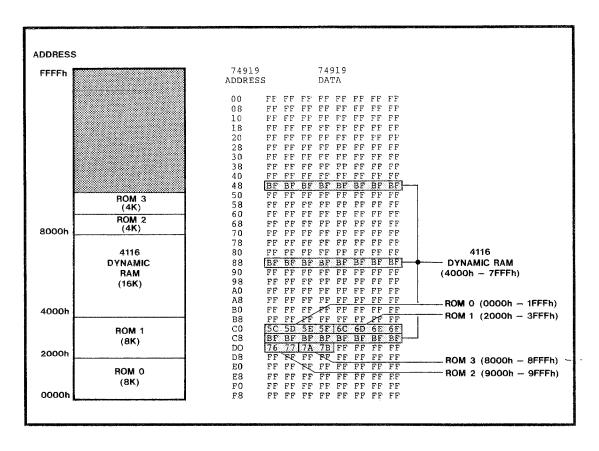

| Figure   |     | Factory Shipped 74919 Contents              | 16           |

| Figure   | 6:  | Resulting IOP Standard Memory Map           | 17           |

| Figure   | 7:  | 74919 Prom Inputs and Outputs               | ī.           |

| Figure   | 8:  | 74919 Map Partitions                        | 19           |

| Figure   | 9:  | First Custom Map and 74919 Data             | 21           |

| Figure   | 10: | Second Custom Map and 74919 Data            | 22           |

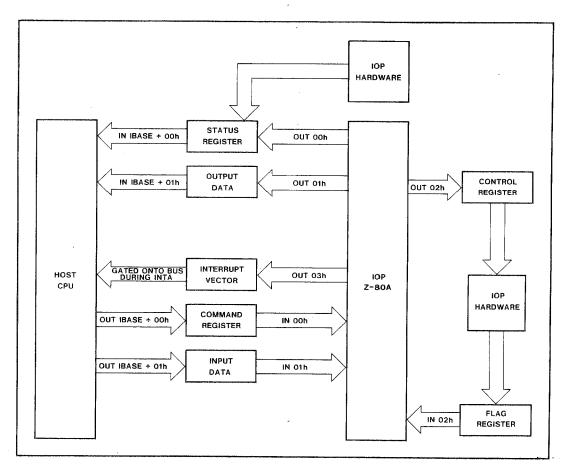

| Figure   | 11: | IOP Register Access                         | 23           |

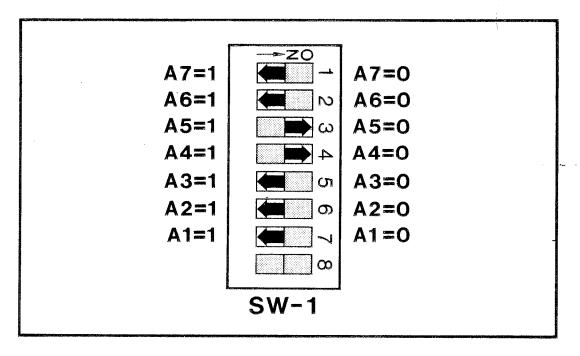

| Figure   | 12: | IOP Base Address Switch, SWl                | 24           |

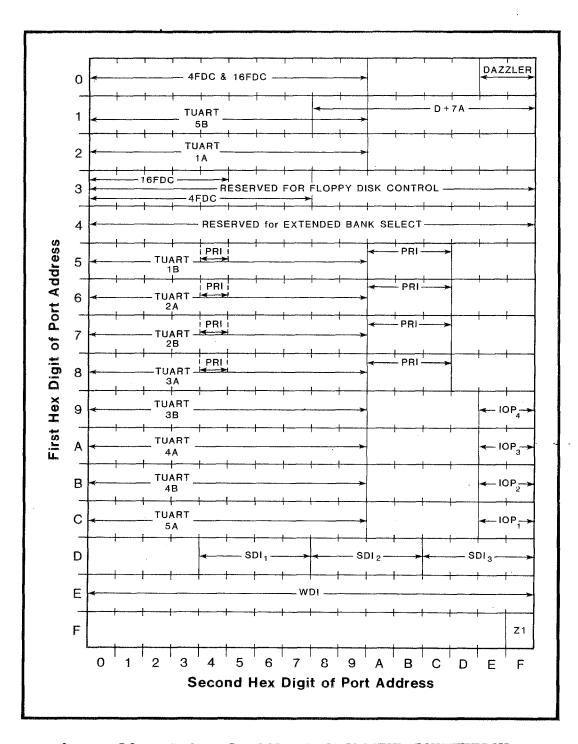

| Figure   | 13: | Cromemco Port Assignment Convention         | 25           |

| Figure   | 14: | IOP Poc and Reset Circuitry                 | 26           |

| Figure   | 15: | IOP Registers After Poc, Reset or Clear     | 28           |

| Figure   | 16: | IOP S-100 Bus Numbering, Dimensions         | 31           |

| Figure   | 17: | IOP Connectors Jl and J2                    | 32           |

| Figure   | 18: | IOP Connector Jl Pin Numbers                | 34           |

| Figure   | 19: | Host Data to IOP                            | 35           |

|          |     | IOP Data to Host                            | 38           |

| Figure   | 21: | Host Commands to IOP                        | 41           |

| Figure   | 22: | IOP Status to Host                          | 44           |

| Figure   | 23: | An Example Custom C-Bus Peripheral Design   | 54           |

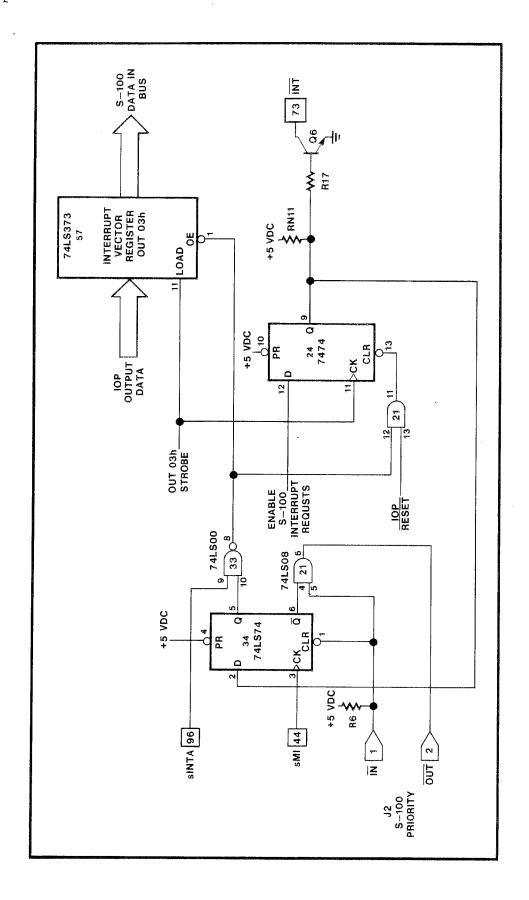

| Figure   | 24: | IOP Interrupt Request Circuitry             | 58           |

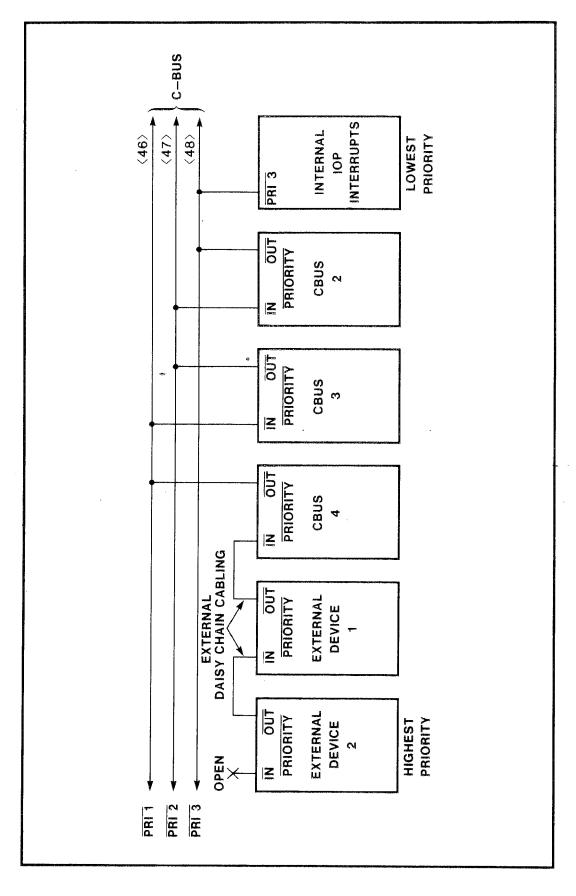

| Figure   | 25: | C-Bus Priorities                            | 62           |

| Figure   | 26: | IOP S-100 Interrupt Circuitry               | 66           |

| Figure   | 27: | S-100 Interrupt Daisy Chain Wiring          | 67           |

| Figure   | 28: | C-Bus DMA Request and Acknowledge Circuitry | 75           |

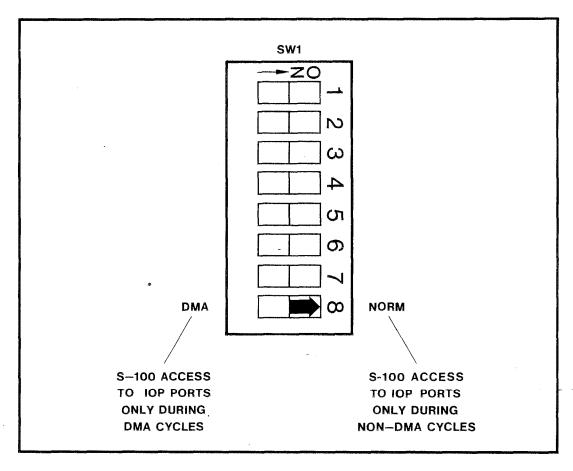

| Figure   | 29: | DMA/Normal Switch                           | 77           |

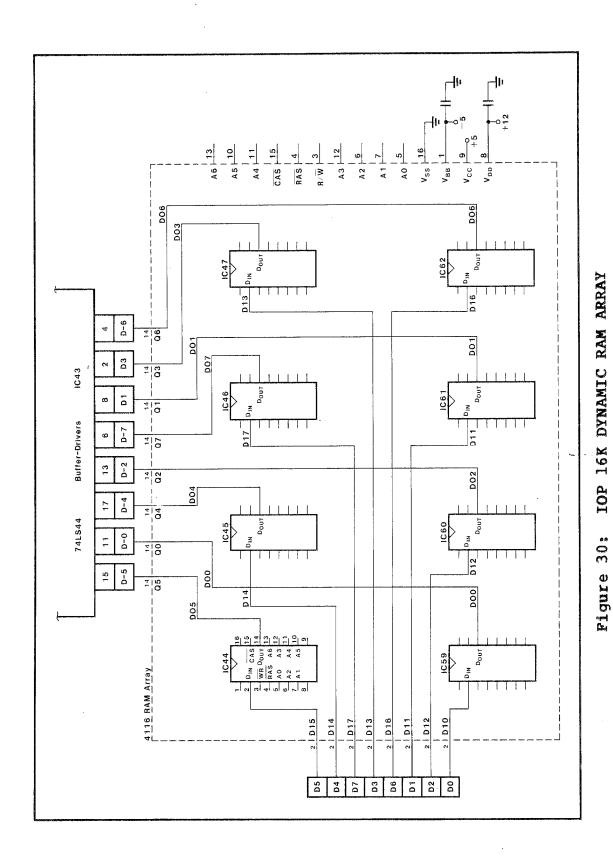

| Figure   | 30: | IOP 16K Dynamic Ram Array                   | 82           |

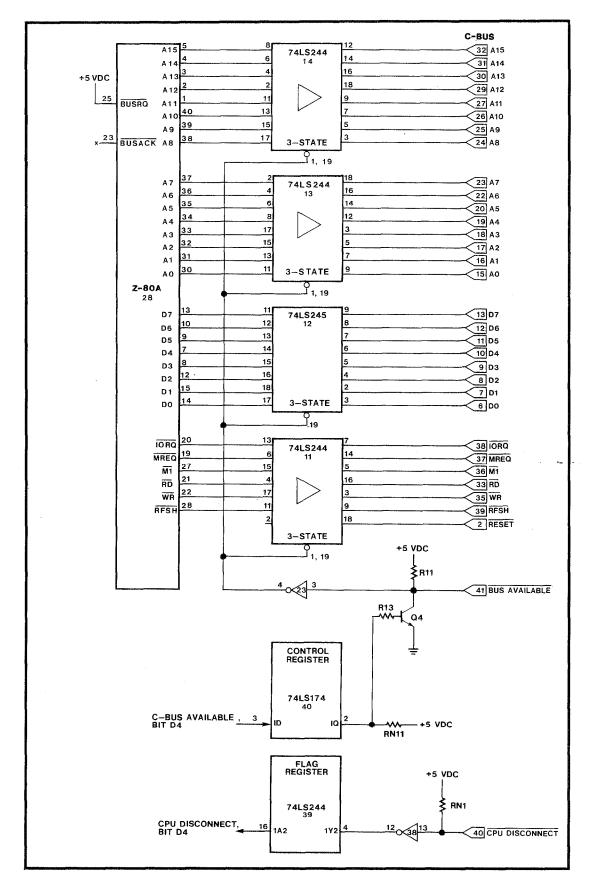

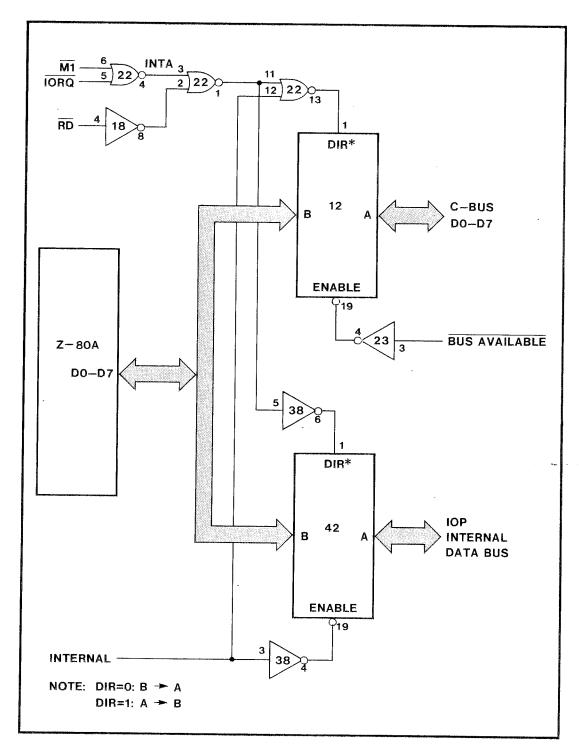

| Figure   | 31: | IOP Internal/External Data Bus Control      | 87           |

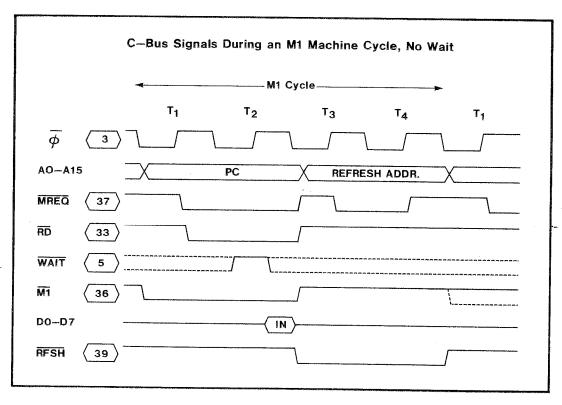

| Figure   | 32: | Ml Cycle, No Wait States                    | 93           |

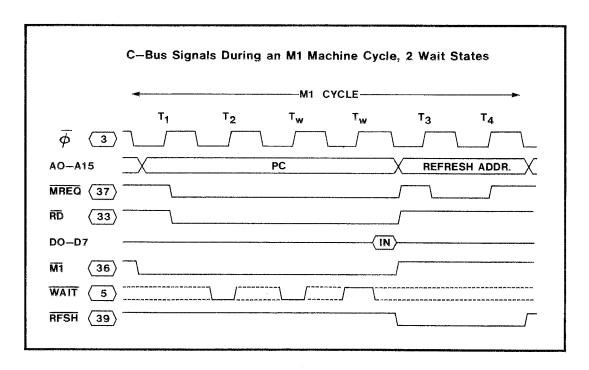

| Figure   | 33: | Ml Cycle, 2 Wait States                     | 94           |

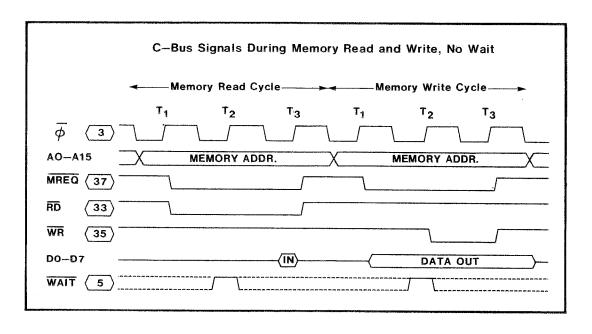

| Figure   | 34: | Memory Read/Write, No Wait States           | 94           |

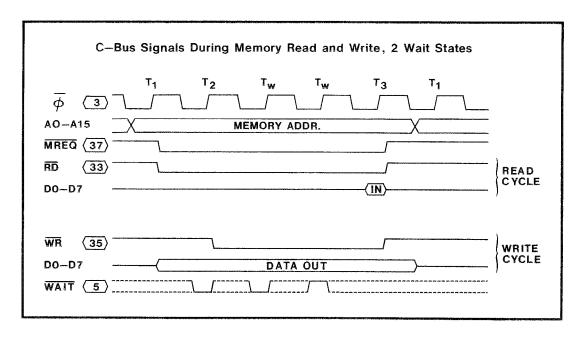

|          |     | Memory Read/Write, 2 Wait States            | 95           |

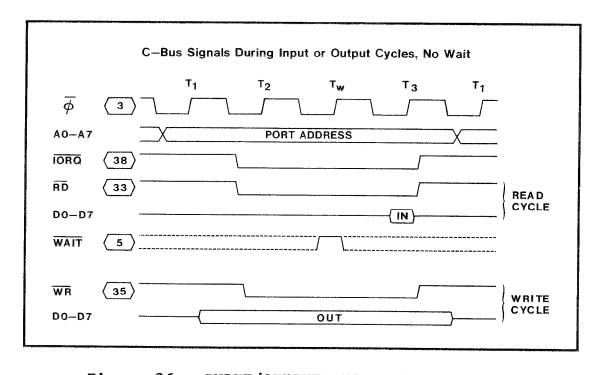

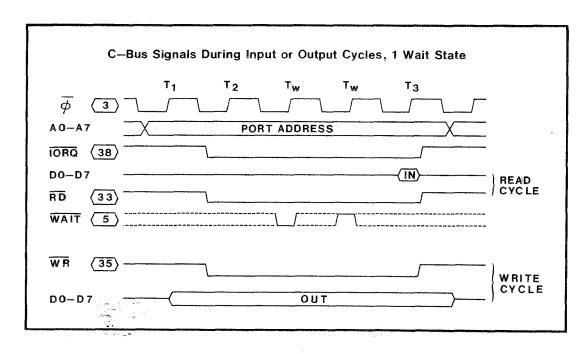

| Figure   | 36: | Input/Output, No Wait States                | 95           |

| Figure   | 37: | Input/Output, l Wait State                  | 96           |

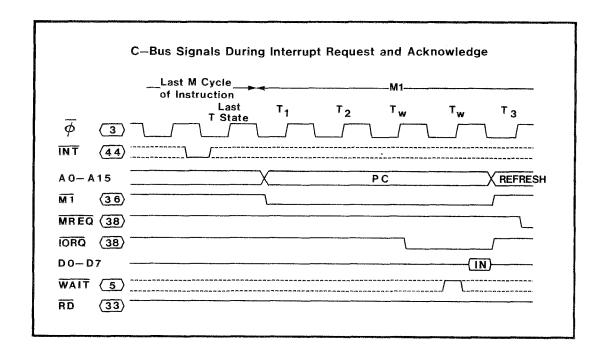

| Figure   | 38: | Interrupt Request and Acknowledge           | 96           |

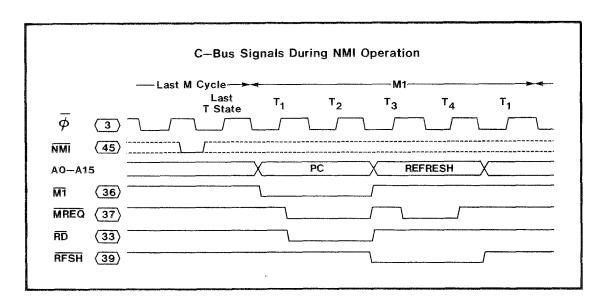

| Figure   | 39: | NMI Cycle                                   | 97           |

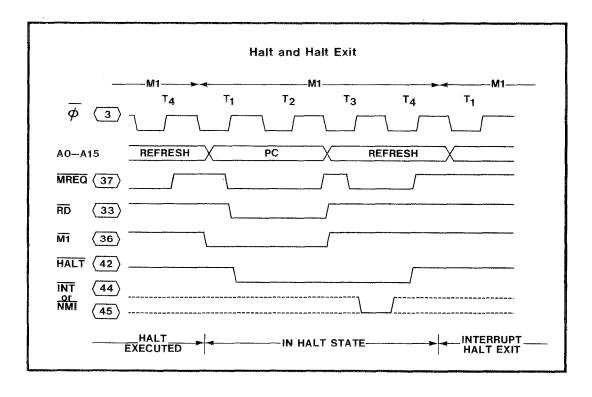

| Figure - | 40: | Halt and Halt Exit                          | 97           |

### TABLES

| Table | 1: | IOP/Host CPU Boundaries      | 11 |

|-------|----|------------------------------|----|

| Table | 2: | IOP ROM Memory Speed Options | 14 |

|       |    | IOP S-100 Bus Connections    | 30 |

| Table | 4: | IOP C-Bus Connections        | 33 |

#### TECHNICAL SPECIFICATIONS

Input/Output Processor

Processor Type: Z-80A

Clock Frequency: 4,000 MHz

Instruction Set: 158 instructions including the 78 member

8080 instruction set

ROM Capacity: Up to 32 Kbytes

ROM Type: Texas Instruments 2516, 2532 EPROM; Texas

Instruments 4732, 4764 masked ROM; Intel 2716, 2732 EPROM, or their generic

equivalents

RAM Capacity: 16 Kbytes

RAM Type: 4116 Dynamic (included)

IOP Registers: All registers I/O mapped; 4 output

(Status, Output Data, Control and Interrupt Vector), 3 input (Command,

Input Data and Flags)

S-100 I/O Ports: 2 output (Command and Input Data), 2

input (Status and Output Data)

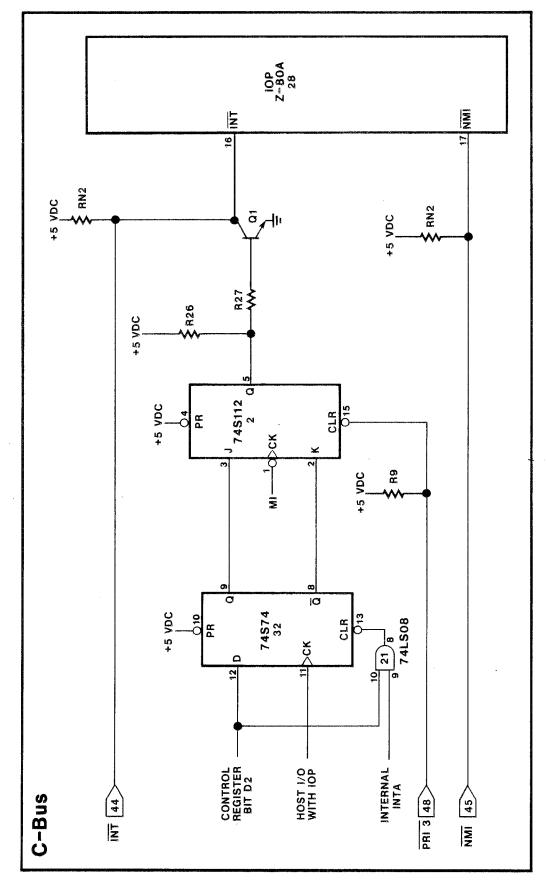

C-Bus Interrupts: Host read/write interrupts and C-Bus

peripheral interrupts daisy chain prioritized; Z-80A interrupt modes IMO,

IMl and IM2 supported

S-100 Bus Interrupts: IOP interrupt requests to host software

controlled; IOP supplies programmable IMO or IM2 vectors; IOP interrupt requests

S-100 daisy chain prioritized

Bus Compatibility: Standard-100 (S-100)

Cromemco Bus (C-Bus)

Power Requirements: +8 VDC @ 1.75 Amps (max)

+18 VDC @ 100 mA (max) -18 VDC @ 50 mA (max)

Operating Environment: 0 - 55 degrees Celsius

#### ABOUT THIS MANUAL

After reading this manual, the reader should be able to install, configure, and verify the proper operation of an IOP board in a host S-100 system. Also, the reader should be able to tailor the IOP configuration options to best suit the system requirements at hand. While this manual provides some IOP programming examples, it is not intended to be a software reference.

Chapter 1 explains Cromemco's C-Bus architecture, and the role the IOP board plays in it. Chapter 2 discusses most IOP hardware features excluding interrupts and DMA operation. An IOP initial checkout procedure appears at the end of Chapter 2. All categories of IOP interrupts are treated in Chapter 3, including interrupt programming examples. Chapter 3 also deals with C-Bus DMA. Chapter 4 analyzes the major IOP hardware subsystems and major signal paths, and it presents C-Bus waveforms for every processor cycle type.

The reader of this manual is assumed to have some knowledge of the Z-80A microprocessor and Z-80 Assembly Language. Throughout the entire manual, positive logic is assumed; reset means logic 0, and set means logic 1 as these terms apply to bit states.

The following two references should prove helpful while reading this manual. The first, which is included in Cromemco's IOP Development Software package, is the primary IOP software reference. It outlines the entire IOP software development cycle, and describes how to operate the IOP utility programs contained in the package. The second describes Cromemco's Quadart board, a powerful four channel serial C-Bus peripheral. Copies may be obtained at your Cromemco dealer.

- 1. Cromemco IOP Development Software Instruction Manual, part number 023-4032

- 2. Cromemco Ouadart Serial Interface Instruction Manual, part number 023-2005

#### Chapter 1

#### INTRODUCTION

The architecture of S-100 systems hasn't changed much since the S-100 bus was introduced in 1975. A typical S-100 system includes a single CPU, its program memory, and peripheral devices interfaced to the bus with one or more I/O boards. The CPU is directly involved in virtually every data exchange and processing task in such systems. Consequently, as system activity increases, the single system CPU is burdened more and more. System response time and throughput suffer as a result. Even the fastest, most efficient CPU must eventually yield when it is required to manage too many peripherals, or process too much data, or both.

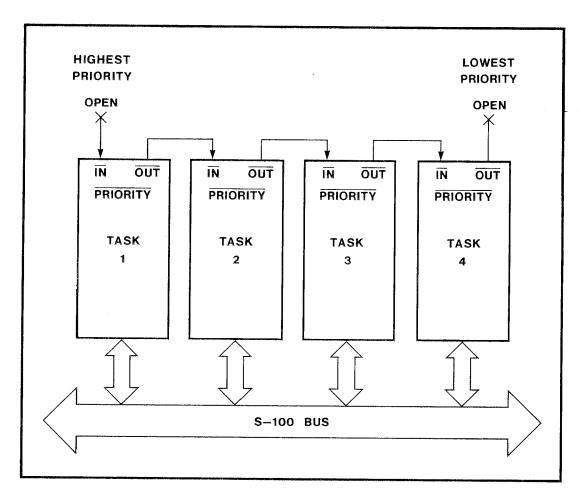

There are two dominant factors which limit S-100 system throughput: a single system CPU, and a fixed bandwidth Any attempt to increase system throughput must simultaneously address both of these limitations. Architectures which have multiple processors may help. If these processors compete with one another for use of the same fixed bandwidth bus to exchange data with their peripherals (e.g., a Multibus-like architecture), then system throughput is only incrementally improved. Ideally, each structured system task which would benefit from intelligent preprocessing and data buffering should have its own dedicated processor and its own dedicated Then, each task processor would manage data transfers to and from its own peripheral(s), perform data buffering, formatting and preprocessing over its own independent expansion bus without competing for use of the main, or host, S-100 bus. As a result, the main, or host, processor would then be substantially offloaded, and free to manage the exchange of preprocessed data between itself and its intelligent system tasks in a structured and efficient manner over the host S-100 bus.

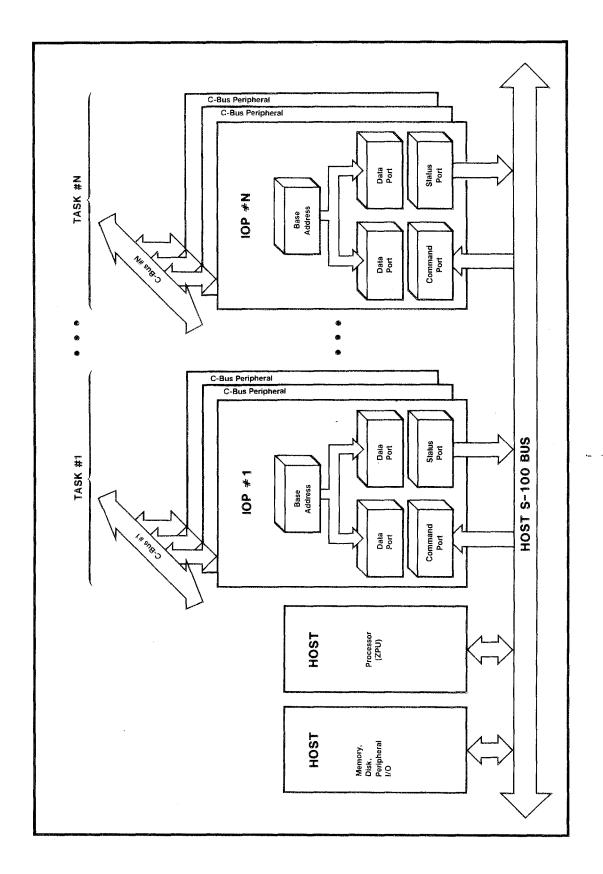

Cromemco's C-Bus architecture is designed to operate in precisely this ideal way; it exploits the inherent advantages of distributed processing, and it simultaneously overcomes the limitations of a fixed bandwidth bus in an S-100 setting. In short, Cromemco's C-Bus architecture brings functional multiprocessing to S-100 bus systems. The basic C-Bus system structure is illustrated in Figure 1.

Figure 1: CROMEMCO'S C-BUS ARCHITECTURE

The figure shows a core S-100 system, consisting of a host S-100 bus, processor, memory and I/O boards, augmented by one or more tasks. Each task consists of an Input/Output Processor (IOP) board, an independent 50 conductor overhead expansion bus (a C-Bus), and the C-Bus peripherals connected to it (note that some tasks require only a single IOP board). The IOPs and C-Bus peripherals are standard dimensioned S-100 boards which occupy slots in the host S-100 bus, and draw power from it.

Each IOP is a single card computer which features a 4 MHz Z-80A CPU, 32 Kbytes of resident firmware (ROM) space, 16 Kbytes of RAM memory, and hardware interfaces to both the S-100 and C-Busses. The S-100 bus interface makes each IOP task look like two parallel I/O ports to the host processor; these ports may be mapped anywhere in the host processor's I/O space. The host passes commands and data to the IOP through the two ports in one direction, and the IOP passes status and preprocessed data back to the host in the other. A significant IOP feature not shown in the figure is the IOP's ability to interrupt the host and pass interrupt vectors to the S-100 bus.

The IOP C-Bus interface consists of a complete group of Z-80A address, data and control lines which gives the IOP and its peripherals full memory access, parallel I/O, interrupt and DMA capabilities without competing in any way with corresponding host S-100 bus functions. This gives the IOP programmer flexibility in designing a task structure for the most efficient gathering and processing of raw data by the IOP and C-Bus peripherals, and then passing the preprocessed data back to the host over the S-100 bus in either a polled or interrupt driven fashion.

The inherent flexibility of Cromemco's C-Bus architecture allows the system designer to create several useful variations on the S-100 system structure just described. For example, one or more IOP tasks and a host system may share the same physical volume, draw power from the same S-100 bus, but perform completely independent functions. Typical functions might include line multiplexing, data concentration, protocol conversion or data conversion performed by an IOP and one or more Quadart boards connected to it. variations include several independent but coresident IOP tasks running without host processor management, or even a stand alone IOP board acting as an intelligent I/O controller (the I/O devices could be controlled either over the IOP S-100 edge connector, or over the IOP's C-Bus interface).

Cromemco supports the growing C-Bus hardware line with a comprehensive set of software/firmware tools for IOP program development. These tools are supplied in Cromemco's IOP Development Software package, Model IDS, which includes:

- 1. **IOPMON,** a 2516 EPROM resident IOP monitor program which occupies IOP socket ROMO.

- 2. IOPEX, an IOP file management executive program which uploads/downloads host disk files to and from IOP memory.

- 3. **IOPDEBUG,** the IOP memory resident debugger program which expands the number of **IOPMON** commands.

- 4. Comprehensive documentation on the programs above, plus several other useful utility routines with documentation.

#### Chapter 2

#### IOP OPERATING INSTRUCTIONS

The IOP is a microprocessor controlled S-100 subsystem which must be viewed and understood in a system context. This chapter first defines that context, and then discusses the major IOP subsystems (except the IOP interrupt and DMA subsystems which are discussed in the following chapter) from an operational point of view. Most of the IOP configuration options are software defined -- see the Control Register and Interrupt Register bit descriptions in Appendix A near the end of this manual for a discussion of these options. The IOP features the following three hardware configuration options:

- Selecting the IOP base address which places the IOP in the host's I/O map -- see Section 2.6,

- 2. Defining the IOP internal memory map with the contents of a memory mapping PROM -- see Section 2.5, and

- 3. Selecting the number of Wait States which are automatically inserted during IOP ROM read cycles -- see Section 2.4.

The IOP is factory shipped with: (1) IOP base address switch SWl set to CFh, the switch setting shown in Figure 12, (2) a memory mapping PROM installed in board socket IC10 which defines the standard IOP memory map shown in Figure 6, and (3) with no Wait State jumper strap installed; this means that all IOP ROMs must have memory access times less than 570 nSec. These factory selected options anticipate the "standard IOP configuration" in which; (1) 2516 EPROM program IOPMON occupies IOP socket ROMO, (2) any additional firmware is programmed into 2516 EPROM devices which occupy IOP sockets ROM1 through ROM3, and (3) IOP ROM memory spans addresses 0000h - 1FFFh (8 Kbytes), and IOP RAM memory spans 4000h - 7FFFh (16 Kbytes). Carefully note that all Cromemco supplied programs in the IOP Development Software package assume that program IOPMON is installed in socket ROMO, and that IOP RAM memory spans 4000h -7FFFh.

The reader is encouraged to exercise a newly purchased IOP board by following the check out procedure presented in Section 2.11, and to study Chapter 2 carefully before changing any of the factory selected configuration options.

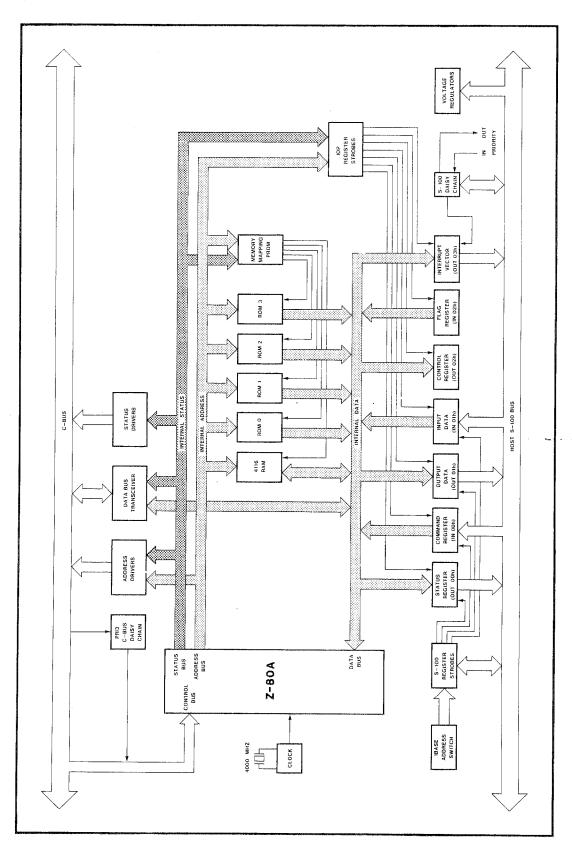

#### 2.1 IOP BLOCK DIAGRAM

The IOP is a single board computer with a Z-80A CPU clocked at  $4.000~\rm MHz$ ,  $16~\rm Kbytes$  of  $4116~\rm dynamic$  RAM memory, socket space for up to  $32~\rm Kbytes$  of ROM memory, seven parallel I/O registers, and hardware interface circuitry to both the S-100 and C-Busses (see Figure 2).

From the viewpoint of the host S-100 bus, the IOP looks like two intelligent parallel I/O ports and a vectored interrupt request source. The two consecutively numbered ports may be switch mapped anywhere in the S-100 bus I/O space. From the viewpoint of peripherals connected to the C-Bus cable, the IOP looks like an intelligent controller which manages the C-Bus address, data and status lines, and which responds to vectored interrupt and DMA requests from the peripherals.

The IOP Z-80A executes program code from its own internal ROM or RAM memory (it can also execute program code from memory which is properly interfaced to its C-Bus cable); this program code in turn coordinates the exchange of data with C-Bus peripherals and the host processor and preprocesses the data traveling in both directions. In short, the program code operationally defines the task which the IOP performs. unregulated +8 VDC to the IOP resets its Z-80A which causes it to automatically begin program execution at address 0000h. This is the starting address of ROMO, assuming the standard memory map. When IOP Monitor program IOPMON occupies this socket, a Power On Clear (POC) sequence automatically starts program IOPMON When the IOP is operated in a Cromix or CDOS host system, the host processor would then typically establish contact with IOPMON, download an IOP application program into IOP RAM memory, and start the program running.

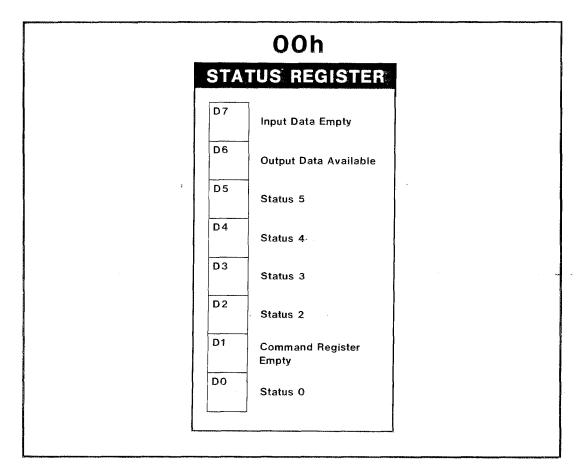

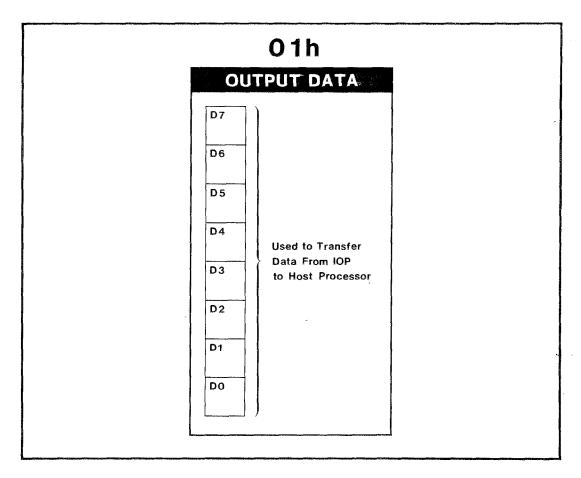

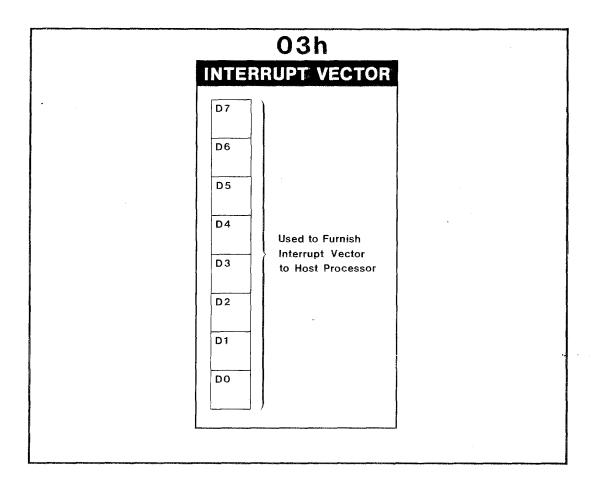

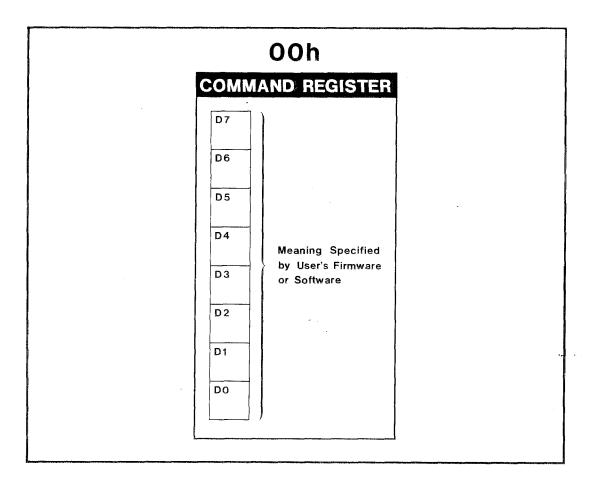

The IOP uses seven internal parallel hardware registers to pass commands, status, interrupt vectors and data to and from the host over the S-100 bus, and also to control certain C-Bus events. The seven registers have fixed port addresses in the IOP's internal I/O map (OUT 00h - OUT 03h, and IN 00h - IN 02h). Four of the seven registers are also accessible to the host processor.

Figure 2: IOP BLOCK DIAGRAM

These four registers are positioned in the host I/O map by IOP base address (Ibase) switch SWl; the resulting port addresses then become OUT Ibase+00h, OUT Ibase+01h, IN Ibase+00h and IN Ibase+01h. Note that IN 00h corresponds to OUT Ibase+00h (Command Register), IN 01h corresponds to OUT Ibase+01h (Input Data), OUT 00h corresponds to IN Ibase+00h (Status Register), and OUT 01h corresponds to IN Ibase+01h (Output Data); that is, data output by the host is input by the IOP, and vice versa. A quick reference listing of the seven registers appears on the manual overleaf. Refer to Section 2.6 and Appendix A for a full discussion of these registers.

#### 2.2 IOP CENTRAL PROCESSING UNIT

The heart of the IOP is its Z-80A Central Processing The Z-80A is an 8-bit CPU which can Unit (CPU). directly address 64 Kbytes of memory (addresses 0000h through FFFFh), 256 input ports and 256 output ports (port addresses 00h through FFh). The Z-80A's 158-member instruction set includes, as a subset, the 8080's 78-member instruction set. The Z-80A is clocked at a fixed, crystal controlled 4.000 MHz, yielding instruction execution times which range between  $1.0\tilde{0}$ uSec (for 4-cycle instructions) to 5.75 uSec (for 23-cycle instructions) assuming that no Wait States are With the exceptions of input BUSRO and output BUSAK, the complete set of Z-80A address, data and control signals are brought out at the IOP C-Bus interface. Note that Z-80A status and control signals are similar to, but not identical with S-100 status and control signals, and that C-Bus peripherals make DMA requests using C-Bus line CPU DISCONNECT, while BUS AVAILABLE serves as an acknowledgment.

The IOP Z-80A may be one of several operating system processors. Consequently, it is important to clearly delineate the boundaries between memories, I/O ports, interrupt and DMA request sources which are associated with each processor. Table 1 shows that the IOP Z-80A manages the C-Bus and the peripherals attached to it, as an isolated system, in much the same way as the host processor manages the S-100 bus.

Table 1

IOP/HOST CPU BOUNDARIES

| EVENT                  | IOP Z-80A                                                 | HOST CPU                                               |

|------------------------|-----------------------------------------------------------|--------------------------------------------------------|

| Memory<br>Reads:       | From Internal IOP<br>Memory Or External<br>C-Bus Memory   | From S-100 Bus<br>Memory                               |

| Memory<br>Writes:      | To Internal IOP<br>Memory And External<br>C-Bus Memory    | To S-100 Bus<br>Memory                                 |

| I/O<br>Reads:          | From Internal IOP<br>Registers Or<br>External C-Bus Ports | From S-100 Bus<br>Ports Including<br>Two IOP Ports     |

| I/O<br>Writes:         | To Internal IOP<br>Registers And<br>External C-Bus Ports  | To S-100 Bus<br>Ports Including<br>Two IOP Ports       |

| Interrupt<br>Requests: | From Internal IOP<br>Events Or C-Bus<br>Peripherals       | From S-100 Bus<br>Peripherals<br>Including the IOP     |

| DMA<br>Requests:       | From C-Bus<br>Peripherals                                 | From S-100 Bus<br>Peripherals Not<br>Including the IOP |

. .

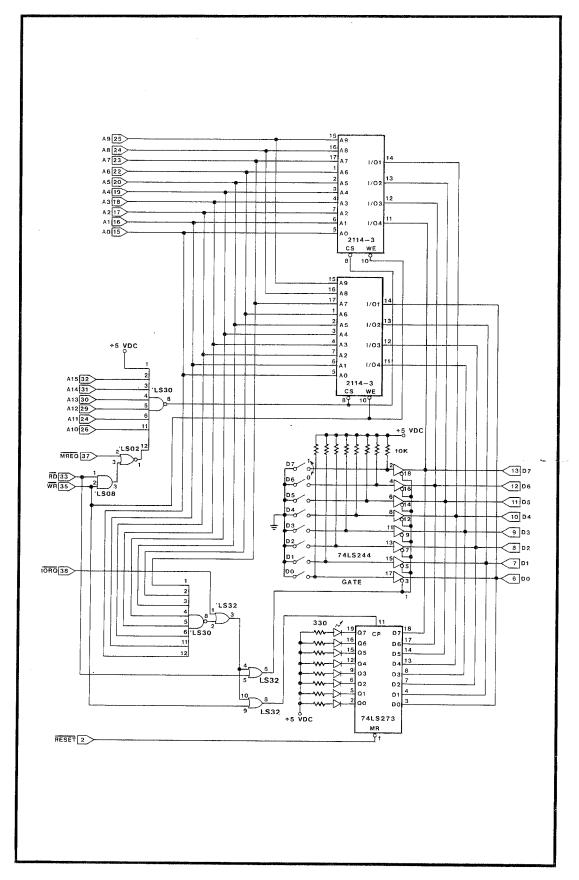

When the IOP Z-80A performs a memory read, then either internal IOP memory (as defined by the memory mapping PROM), or external C-Bus memory, is accessed. If internal and external memory addresses overlap, then IOP circuitry detects the conflict and routes only internal IOP memory data to the Z-80A. Memory writes, on the other hand, are performed to internal and external overlapping memory in parallel. Likewise, when the IOP Z-80A performs an I/O read, then either internal registers IN 00h through IN 02h, or external C-Bus ports are accessed. Again, overlapping port address reads are resolved in favor of internal IOP registers. IOP Z-80A I/O writes are directed to internal IOP registers OUT 00h through OUT 03h, and external C-Bus ports in parallel. The IOP Z-80A maskable INT pin may be driven active low either by internal IOP events (see Section 3.1), or by any C-Bus peripheral. Any C-Bus peripheral may make a software polled DMA request to the IOP Z-80A by driving C-Bus line CPU DISCONNECT active low (see Section 3.4).

#### 2.3 IOP RAM MEMORY

The IOP is shipped with 16 Kbytes of read/write spanning addresses 4000h - 7FFFh. Refer to Section 2.5 for instructions on how to locate the RAM memory block elsewhere in the IOP memory map. IOP RAM memory physically consists of eight 4116 (16K x 1) dynamic RAM memory chips occupying sockets IC44 through IC47, and IC59 through IC62. IOP application programs with critical speed requirements should be loaded in, and run from IOP RAM memory since no CPU Wait States are inserted for these 150 nSec (max) memory access parts.

The 4116 dynamic memory chip must be refreshed periodically to maintain its data integrity. transparent refresh technique is used on the IOP; that is, the seven bit refresh address supplied by the Z-80A during T2 and T3 of each M1 fetch cycle (while the Z-80A address bus is not being used for other purposes) is multiplexed onto all 4116 address lines and strobe RAS is pulsed low. Each such RAS only refresh cycle causes 128 bits of each 4116 device to be read and written back to their memory bit cells. An entire 4116 device is completely refreshed when the Z-80A has supplied 128 sequential RAS only refresh cycles. The 4116 must be completely refreshed every 2 mSec, or its data integrity is not guaranteed. The only way this requirement might not be met on the IOP is when the C-Bus WAIT line, <5>, is held active low for extended periods. This active signal holds off further Z-80A Ml cycles, and also refresh addresses as a consequence. Refer to Section 4.4 for a detailed discussion of this topic.

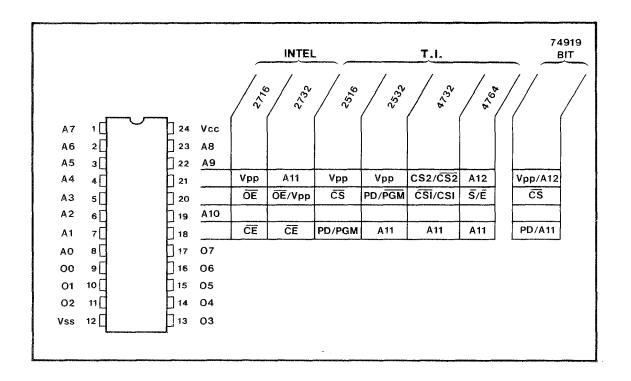

#### 2.4 IOP ROM MEMORY

The IOP provides sockets ROMO through ROM3 which may be occupied by 24-pin ROM devices conforming to the pin out shown in Figure 3. A unique memory mapping PROM allows a mix of device types to be plugged into the four sockets by supplying the high order address and control signals required by each device type. In addition, the memory mapping PROM locates the ROM sockets and the 16 Kbyte block of RAM memory in the internal IOP memory map. The factory shipped memory mapping PROM configures sockets ROMO through ROM3 for TI 2516 (or Intel 2716) type devices, and it locates the four devices at 0000h-lFFFh in the IOP memory map (see Figure 6). This arrangement anticipates that 2516 program IOPMON will occupy IOP socket ROMO in most applications.

Figure 3: IOP ROM PIN OUTS

The IOP user may wish to program a custom memory mapping PROM to accommodate other ROM device types, and other map structures, in dedicated IOP applications. Section 2.5 describes how to determine the required memory mapping PROM contents for all of the following ROM devices, or their generic equivalents: Texas Instruments 2516 and 2532 EPROMs; Intel 2716 and 2732 EPROMs; Texas Instruments 4732 and 4764 masked ROMs.

All, none, or any combination of IOP ROM sockets may be occupied. Performing a memory read from an empty ROM socket almost always returns OFFh data (all logic 1 bits from floating data bus lines). Writing to an empty IOP ROM socket has no affect other than consuming time, but writing to an occupied ROM socket should be avoided to preclude internal data bus conflicts between Z-80A write data and ROM read data.

The IOP provides three ROM memory speed options. The three options provide for: (1) inserting one Z-80A Wait State on every IOP ROM read cycle -- the factory shipped option, or (2) inserting one Z-80A Wait State on each Ml

(memory fetch) cycle to IOP ROM memory, and inserting no Wait States on non-M1 cycles, or (3) inserting no Z-80A Wait States when reading IOP ROM memory. Note that regardless of the option selected, no Wait States are inserted during any IOP RAM read/write cycle, nor during any read/write cycle to external C-Bus memory. selected option applies to all IOP ROM memory. Thus, when fast and slow ROM memory are mixed on the IOP, the option must meet the speed requirements of the slowest Table 2 below shows the required ROM memory used. maximum memory access times (address to valid data) when using each option. The No Wait States option is using each option. The No Wait States option is described only to anticipate future ROM speed improvements.

Table 2: IOP ROM MEMORY SPEED OPTIONS

#### MAXIMUM MEMORY ACCESS TIME (nSec)

| ONE WAIT STATE INSERTED: | NEVER | M1 CYCLES<br>ONLY | ALL READ<br>CYCLES |

|--------------------------|-------|-------------------|--------------------|

| 2 Kbyte ROMs:            | 320   | 430               | 570                |

| 4 Kbyte ROMs:            | 240   | 350               | 490                |

| 8 Kbyte ROMs:            | 240   | 350               | 490                |

The options are selected by properly wiring the two solder jumper pads labeled M2 on the IOP silk screen legend (see Figure 4). The IOP is shipped with no jumper installed which selects one Wait State on all IOP ROM read cycles so that the common 450 nSec 2516/2716 type EPROM may be used. If one of the other two options is desired, then the large plate heat sink must be removed to gain access to the solder pads below; loosen the three heatsink securing screws on the board solder side, then slide the slotted-guide heatsink assembly off the board.

Install a jumper strap between the two pads to select the **one Wait State each M1 cycle** option. To select the **no Wait States** option, connect the left pad (the one shown connected to IC4 pin 1) to any convenient ground point (like IC4 pin 7). Replace the heatsink when done.

Figure 4: IOP ROM SPEED JUMPER PADS

#### 2.5 IOP MEMORY MAPPING PROM

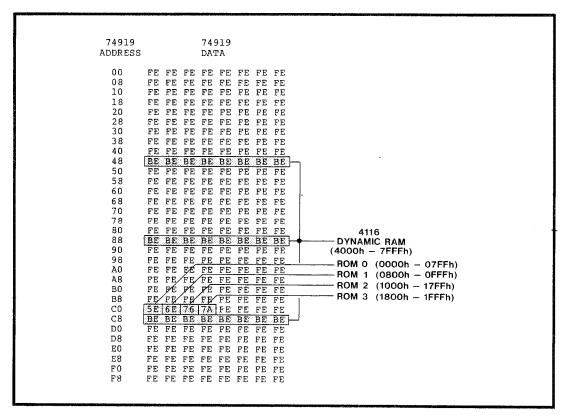

The IOP's memory mapping 74919 PROM (IC10 in the IOP Schematic Diagram) defines the IOP memory map. The factory shipped 74919 contents are shown in Figure 5 (all values shown in hexadecimal), and the resulting standard IOP memory map is shown further below in Figure 6. The following paragraphs describe how to program 74919 PROMs to accommodate different ROM device types, and to produce other IOP memory maps. The reader may skip this section entirely if the standard memory map is used.

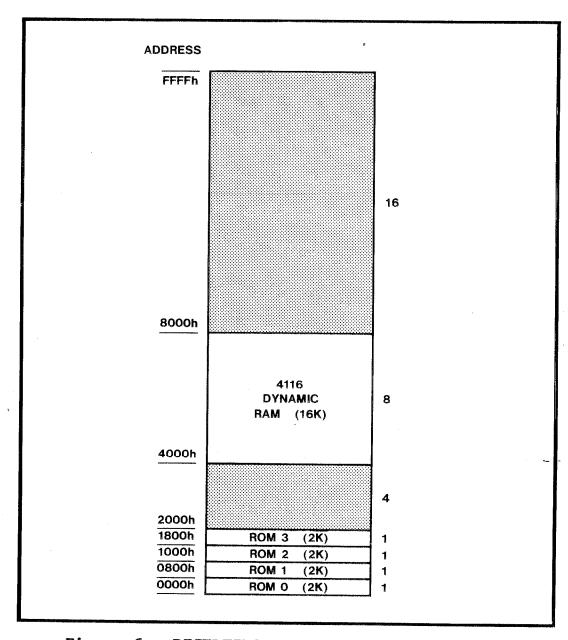

Figure 5: FACTORY SHIPPED 74919 CONTENTS

Figure 6: RESULTING IOP STANDARD MEMORY MAP

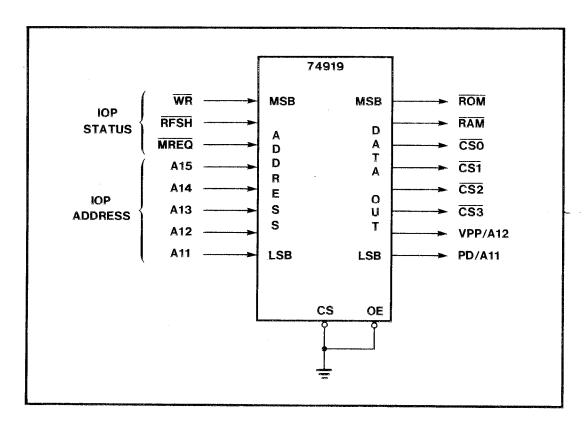

The basic function of the 74919 is to convert IOP address and status input data into RAM and ROM select output data by means of its programmed contents. Figure 7 shows that a unique 74919 byte is addressed for every combination of IOP control bus lines  $\overline{WR}$ ,  $\overline{RFSH}$ ,  $\overline{MREQ}$  and address lines Al5 - All. Since only Al5 through All are used as inputs, each programmed 74919 byte corresponds to a 2 Kbyte block of internal IOP memory (individual bytes are addressed by AlO - AO). If, for example,  $\overline{WR}$  = 0,  $\overline{RFSH}$  = 1,  $\overline{MREQ}$  = 0, Al5 = Al4 = Al3 = 0 and Al2 = Al1 = 1, then the IOP Z-80A is performing a memory ( $\overline{MREQ}$  = 0) write cycle ( $\overline{WR}$  = 0) to memory block 1800 - 1FFF.

Figure 7: 74919 PROM INPUTS AND OUTPUTS

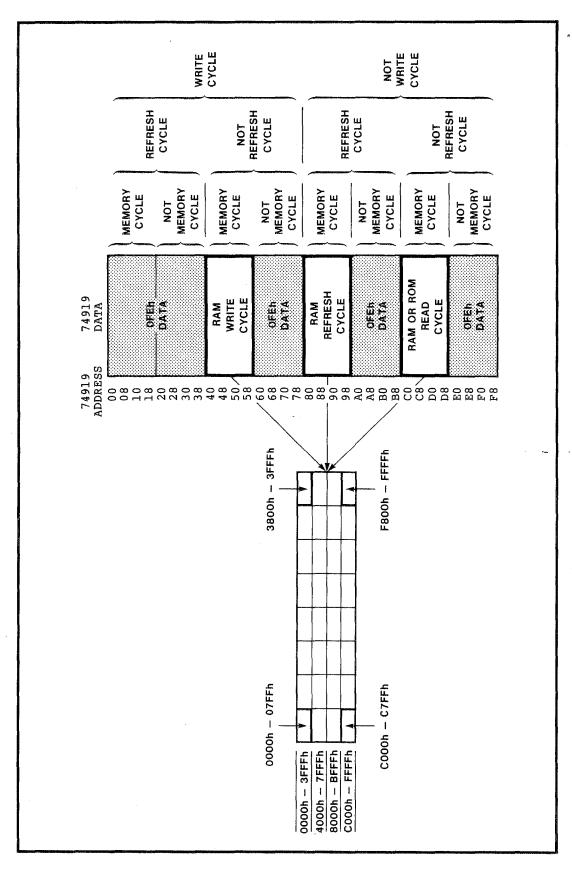

Status signals  $\overline{\text{WR}}$ ,  $\overline{\text{RFSH}}$  and  $\overline{\text{MREQ}}$  drive the 74919 high order address lines, and consequently they partition the 74919 memory map into the eight regions shown to the right in Figure 8. Of the eight regions, only three correspond to actual IOP memory cycles:  $\overline{\text{WR}} = 0$ ,  $\overline{\text{RFSH}} = 1$  and  $\overline{\text{MREQ}} = 0$  for RAM write cycles;  $\overline{\text{WR}} = 1$ ,  $\overline{\text{RFSH}} = 0$  and  $\overline{\text{MREQ}} = 0$  for RAM refresh cycles; and  $\overline{\text{WR}} = 1$ ,  $\overline{\text{RFSH}} = 1$  and  $\overline{\text{MREQ}} = 0$  for RAM or ROM read cycles.

Figure 8: 74919 MAP PARTITIONS

IOP address lines Al5 through All further partition the 74919 map as shown to the left in Figure 8. Each of the three regions mentioned above spans the entire 64 Kbyte memory address space with 32 programmable bytes, making each byte correspond to a different 2 Kbyte memory Reference to Figure 7 shows that the 74919 supplies eight memory select output data bits for each input combination. Bit ROM is programmed to logic 0 only if a ROM chip resides at the addressed 2 Kbyte block. In this case, one of the four ROM chip select bits,  $\overline{\text{CSO}}$  through  $\overline{\text{CS3}}$  , would also be programmed to logic 0 to enable the chip's socket, ROMO through ROM3. If, in addition, a 32 (or 64) Kbit ROM is used, then two (or four) consecutive 74919 bytes would be programmed with bit  $\overline{ROM} = 0$ ,  $\overline{CS} = 0$  (the same chip select line in all bytes), and with bit All (and Al2) progressing through a binary count to access successive 2 Kbyte blocks of memory on the ROM chip. Note that ROM memory would typically be mapped into the lowest 2 Kbyte region of the IOP memory map anticipating automatic program start up after a POC.

Bit PD/All serves as a Power Down input on 2516 type devices, and as an All address line on 4 and 8 Kbyte ROMs. If any 2516 type EPROMs are used on the IOP, then all 74919 PD/All bits must be programmed to logic 0. This means that either all or none of the IOP ROMs must be 2516 type devices. Programming all PD/All bits to logic 0 permanently enables all 2516 type devices, and as a result, the 2516 address to data access time limits the ROM memory access speed. If, on the other hand, the PD/All line were to be strobed low as a 2516 is addressed, then the PD low to data access time would limit the ROM memory access speed far below the 2 Kbyte ROM values listed in Table 2 above.

Bit  $\overline{\text{RAM}}$  is programmed to logic 0 only if internal IOP 4116 dynamic memory resides as the addressed 2 Kbyte memory block. In this case, eight sequential 74919 bytes should be programmed with  $\overline{\text{RAM}} = 0$ ; the same address positions in 74919 partitions  $\overline{\text{RAM}}$  write cycles,  $\overline{\text{RAM}}$  refresh cycles and  $\overline{\text{RAM}}$  read cycles must also be programmed with bit  $\overline{\text{RAM}} = 0$ . When bit  $\overline{\text{RAM}}$  is programmed to logic 0, all other bit positions in the same byte should be programmed to logic 1 except when 2516 type devices are used; then PD/All should be programmed to logic 0.

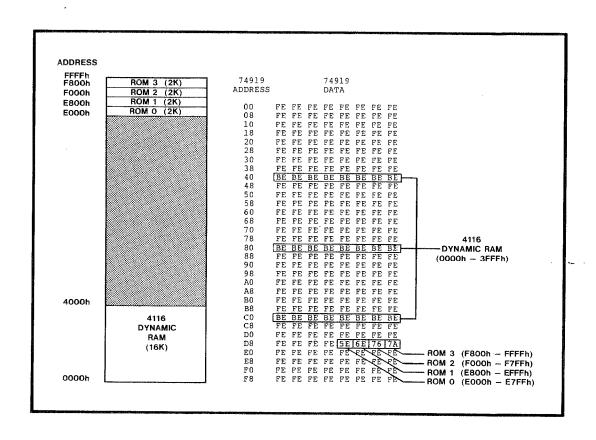

#### Example

Assume that internal IOP memory is to consist of 4116 dynamic RAM memory from 0000h - 3FFFh and four 2516 EPROMs in sockets ROMO through ROM3 spanning E000h - FFFFh. A 74919 bipolar PROM would then be programmed with the data shown in Figure 9, and inserted in IOP socket IC10 to yield the IOP memory map shown in the same figure.

Figure 9: FIRST CUSTOM MAP AND 74919 DATA

#### Example

Assume that internal IOP memory is to consist of two 4764 masked ROMs spanning 0000h - 3FFFh in sockets ROMO and ROM1, then 4116 dynamic RAM memory from 4000h - 7FFFh, then two 4732 masked ROMs spanning 8000h - 9FFFh in sockets ROM2 and ROM3. The 74919 PROM contents and resulting memory map are shown below in Figure 10.

Figure 10: SECOND CUSTOM MAP AND 74919 DATA

#### 2.6 IOP I/O REGISTERS

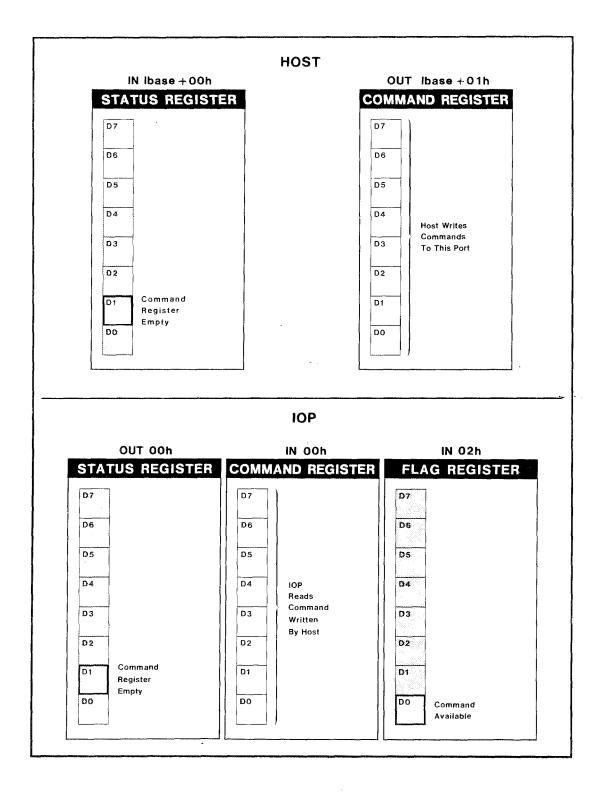

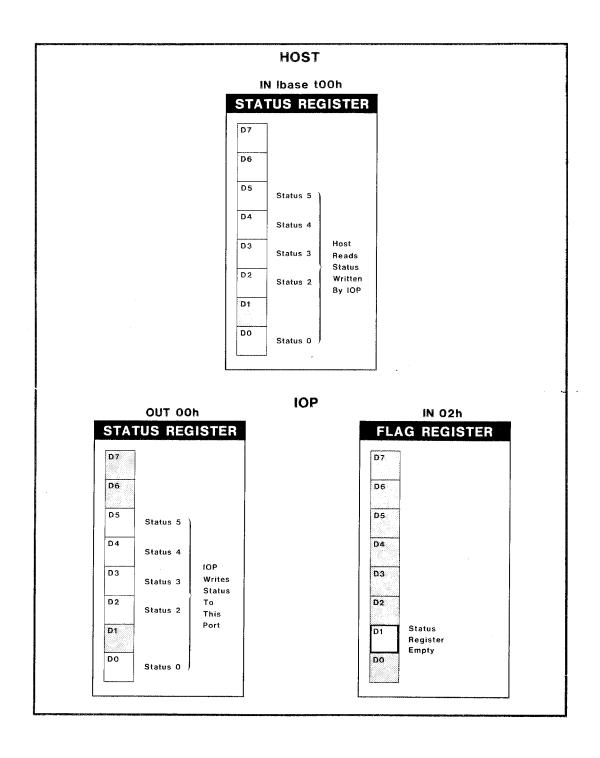

Seven internal IOP registers are provided to: exchange data, status and commands between the IOP Z-80A and the host processor, (2) supply interrupt vectors in response to Interrupt Acknowledge cycles from the host processor, and (3) manage C-Bus DMA requests and The IOP Z-80A has input/output access acknowledgments. to all seven registers, while the host processor has direct input/output access to only four: Status Register, Output Data, Command Register, and Input Data (see manual overleaf for register summary). The port addresses of these seven registers are fixed in the internal IOP I/O map (IN 00h - IN 02h, and OUT 00h - OUT 03h), but are switch located in the S-100 bus I/O map. This arrangement is illustrated in Figure 11.

Figure 11: IOP REGISTER ACCESS

IOP switch SWl defines the IOP Base Address (or Ibase) in the host I/O map. The seven address switches (A7 is the MSB and Al is the LSB) generate 128 even Ibase values (IOP hardware assumes A0=0). Figure 12 shows SWl set to make Ibase = CEh; the host processor would then communicate with the IOP using I/O ports CEh and CFh.

Figure 12: IOP BASE ADDRESS SWITCH, SWI

All Cromemco host resident IOP software assumes that Ibase is CEh for single IOP systems; BEh, AEh and 9Eh are assumed in sequence for multiple IOP systems. In addition to IOP port assignments, Figure 13 illustrates the port numbering convention assumed in all Cromemco supplied software. It is strongly recommended that the IOP user follow this port numbering.

Figure 13: CROMEMCO PORT ASSIGNMENT CONVENTION

The labels assigned to individual IOP register bits are shown on the manual overleaf. Appendix A discusses each bit function in detail, so that material will not be repeated here. Section 2.9 illustrates through programming examples how to use the Status Register, Output Data, Command Register, Input Data and Flag Register to establish and manage a communication link between the host and IOP without using interrupts. Section 3.3 illustrates how the Control Register and Interrupt Vector Register are used in an interrupt driven host/IOP link. Section 3.4 discusses Control Register functions which relate to C-Bus DMA transfer.

#### 2.7 IOP RESET AND POWER ON CLEAR STATE

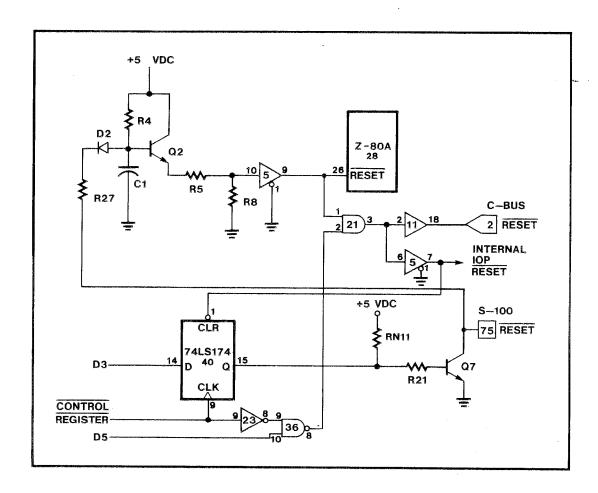

Three sources may reset the IOP board (see Figure 14):

- 1. A Power On Clear (POC), or

- 2. Setting Control Register bit S-100 Reset (D3), or

- Setting Control Register bit C-Bus Clear (D5).

Figure 14: IOP POC AND RESET CIRCUITRY

Applying +8 VDC (unregulated) to the IOP board causes Cl, R4, Q2 and associated circuitry to generate a momentary low level POC pulse at IC5 pin 9. This pulse resets the IOP Z-80A, resets the IOP internal circuitry (see Figure 15), and forces C-Bus line RESET active low.

Outputting a byte to the **Control Register** with bit **S-100 Reset** (D3) set forces S-100 bus line RESET active low and again forces IC5 pin 9 low momentarily. This level again resets the IOP's Z-80A, resets the IOP internal circuitry (including bit **S-100** Reset at IC40 pin 1 -- see Figure 15), and forces C-Bus line RESET active low.

Outputting a byte to the **Control Register** with bit **C-Bus Clear** (D5) set generates a momentary low level at IC36 pin 8. This level resets the IOF internal circuitry (see Figure 15) and forces C-Bus line RESET active low. Unlike the previous two cases, the IOP's Z-80A is **not** reset, so IOP program execution continues uninterrupted.

Figure 15 illustrates the effect that any one of these three reset sources has on the IOP internal circuitry. Register bits which are not affected appear with ? entries (random after a POC and unaltered by a S-100 Reset and C-Bus Clear), and n/a entries mean not applicable.

The IOP Z-80A is reset by either a POC or by setting Control Register bit S-100 Reset, as mentioned above. The Z-80A responds to an active low level on its  $\overline{\text{RESET}}$  pin by:

- disabling maskable interrupts,

- resetting its I-Register (IM2 Interrupt Address Register) to 00h,

- 3. resetting its R-Register (Refresh Address Register) to 00h,

- 4. activating IMO (Interrupt Mode 0), and

- 5. commencing program execution at IOP memory location 0000h.

2. IOP Operating Instructions

| OOh                                                                                                                                | 01h                                                                | 02h                                                                                                                                                                | 03h                                          |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| STATUS REGISTER                                                                                                                    | OUTPUT DATA                                                        | CONTROL REGISTER                                                                                                                                                   | R INTERRUPT VECTO                            |

| D7 1 Input Data Empty  0 Output Data Available  D5 0 Status 5  D4 0 Status 4  D3 0 Status 3  Command Register Empty  D0 0 Status 0 | D7 ? D6 ? D5 ? D4 ? Data From IOP to Host Processor D2 ? D1 ? D0 ? | D7 n/a Not Used D5 n/a Not Used D5 0 C-Bus Clear D4 0 C-Bus Available D3 0 S-100 Reset D2 Enable IOP interrupts D1 0 Gear S-100 Reset Latch D0 0 Interrupt Request | D7 P D6 P D5 P D4 P D3 P D2 P D1 P D0 P D0 P |

|                                                                                                                                    |                                                                    |                                                                                                                                                                    |                                              |

| OOh<br>OMMAND REGISTER                                                                                                             | IOP INPL<br>01h<br>INPUT DATA                                      | IT PORTS  02h  FLAG REGISTER                                                                                                                                       | 03h<br>NOT USED                              |

Figure 15: IOP REGISTERS AFTER POC, RESET OR CLEAR

A ROM resident initialization routine would typically be mapped to begin at IOP memory location 0000h in end product applications which require automatic start up after power is applied (see Sections 2.4 and 2.5).

The IOP can reset the host system by forcing S-100 bus line RESET low, but the host system cannot reset the IOP. In particular, the IOP cannot be reset by either S-100 bus line RESET nor by S-100 bus line POC; the IOP generates its own POC strobe. The IOP may determine that an S-100 bus reset has occurred by polling Flag Register bit Reset Request, however, and optionally reset itself in response. This flexible arrangement assures that critical IOP controlled I/O operations are not interrupted by S-100 bus resets.

# 2.8 IOP CONNECTORS, PIN OUTS AND CABLES

There are three connectors on the IOP board: (1) an S-100 bus edge connector, (2) J1, a 50-conductor C-Bus connector, and (3) J2, a 2-conductor S-100 bus daisy chain connector.

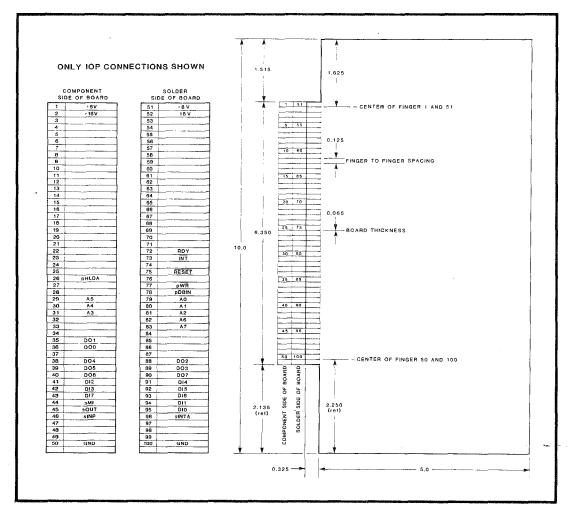

Table 3 lists the S-100 bus signal lines which are used by the IOP, and Figure 16 shows the physical pin numbering convention. The subset of S-100 bus lines used is sufficient for passing I/O data between the host CPU and the IOP, for supplying interrupt requests and vectors to the host CPU, and for supplying power to the IOP. S-100 bus lines which are not connected to the IOP appear with dashed (---) entries in the table.

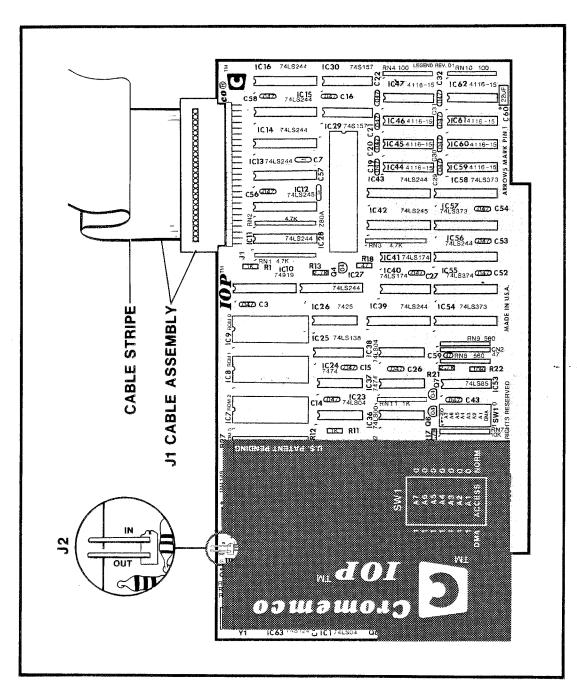

C-Bus cabling connects to the IOP board at Jl as shown in Figure 17. The C-Bus cable assembly physically consists of a 50-conductor ribbon cable and with either two plugs (an IOP and one C-Bus peripheral -- part number 519-0100), four plugs (an IOP and up to three C-Bus peripherals -- part number 519-0063), and five plugs (an IOP and up to four C-Bus peripherals -- part number 519-0101).

Table 4 lists C-Bus signal names with matching pin numbers. All references to  ${\bf GND}$  in the table imply a direct connection to S-100 bus line GND, at 0 VDC potential, and again, dashed table entries mean no connection exists.

Table 3: IOP S-100 BUS CONNECTIONS

Figure 16: IOP S-100 BUS NUMBERING, DIMENSIONS

Figure 17: IOP CONNECTORS J1 AND J2

Table 4: IOP C-BUS CONNECTIONS

| Pin    | Signal            | Pin  | Signal                   |

|--------|-------------------|------|--------------------------|

| <1>    | GND               | <26> | A10                      |

| <2>    | RESET             | <27> | All                      |

| <3>    | $\overline{\phi}$ | <28> | GND                      |

| <4>    | GND               | <29> | A12                      |

| <5>    | WAIT              | <30> | A13                      |

| <6>    | D0                | <31> | A14                      |

| <7>    | Dl                | <32> | A15                      |

| <8>    | D2                | <33> | RD                       |

| <9>    | D3                | <34> | GND                      |

| <10>   | D4                | <35> | WR                       |

| <11>   | <b>D</b> 5        | <36> | MI                       |

| <12>   | D6                | <37> | MREO                     |

| <13>   | D7                | <38> | IORQ                     |

| <14>   | GND               | <39> | RFSH                     |

| <15>   | A0                | <40> | CPU DISCONNECT           |

| <16>   | Al                | <41> | BUS AVAILABLE            |

| <17>   | A2                | <42> | HALT                     |

| <18>   | A3                | <43> | GND                      |

| · <19> | A4                | <44> | ĪNT                      |

| <20>   | A5                | <45> | NMI                      |

| <21>   | GND               | <46> | STREET SPECIAL PRINCIPAL |

| <22>   | A6                | <47> | record about when        |

| <23>   | A7 -              | <48> | PRI 3                    |

| <24>   | A8                | <49> |                          |

| <25>   | A9                | <50> | GND                      |

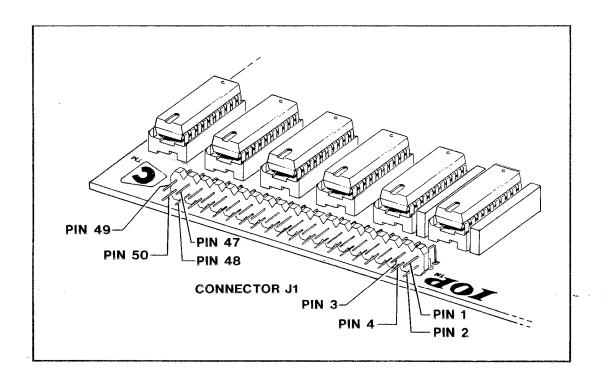

Figure 18 shows the pin numbering convention used for IOP connector Jl. Section 4.11 discusses C-Bus signals and waveforms in detail. Note that S-100 bus lines are called out in Table 3 with square brackets ([]) and C-Bus lines in Table 4 with angular brackets (<>). This convention will be used consistently throughout the manual to avoid confusion over duplicate bus line names.

Figure 17 above shows the location of IOP connector J2 which brings out two lines: S-100 bus daisy chain  $\overline{PRIORITY}$  OUT and  $\overline{PRIORITY}$  IN . Section 3.2 discusses how to use this connector to define the IOP interrupt task priority among other S-100 bus tasks.

Figure 18: IOP CONNECTOR J1 PIN NUMBERS

# 2.9 IOP/HOST COMMUNICATION

This section illustrates with the help of a few simple programming examples, how the host and IOP exchange data, commands, and status. Both IOP and host interrupts are assumed disabled in all examples; interrupts are treated fully below in Chapter 3. Refer to Appendix A for complete descriptions of all IOP register bits used in the programming examples, and Cromemco's IOP Development Software Instruction Manual for instructions on creating, downloading, debugging and executing the programs. The first example program shows how the host sends data to the IOP.

DATA: HOST -> IOP

| IN Ibase +00h STATUS REGISTER                                 | HOST | OUT Ibase + 01h INPUT DATA                                   |

|---------------------------------------------------------------|------|--------------------------------------------------------------|

| D7 Input Data Empty D6 D5 D4 D3 D2 D1                         |      | D7 D6 D5 D4 Host Writes Data To This Port  D2 D1 D0          |

| IN O1h INPUT DATA  D7 D6 D5 D4 IOP Reads Data Written By Host | IOP  | IN 02h FLAG REGISTER  D7 D6 Input Data Available D5 D4 D3 D2 |

| DO                                                            |      | DO                                                           |

Figure 19: HOST DATA TO IOP

Figure 19 shows the IOP register bits used in the data transfer. Two program segments appear below: resides in host memory beginning at 100h, the beginning of the user program area assuming a CDOS operating system; and the second resides in IOP memory beginning at 4000h, the start of IOP RAM assuming the standard memory map. The host program sends the contents of RAM buffer HBUFFO to the IOP by polling Status Register bit Input Data Empty until set, then outputting a single character to register Input Data, then polling bit Input Data Empty again, sending another character, and so on. The IOP program receives each character by polling Flag Register bit Input Data Available until set, then inputting a single character from register Input Data, then polling bit Input Data Available again, reading another character, and so on. Each character read by the IOP is stored sequentially in IOP RAM buffer IBUFFO.

CROMEMCO 280 Macro Assembler version 03.07

|        |          | 0001<br>0002<br>0003 | ;       | HOST PR | OGRAM 1       |                                |

|--------|----------|----------------------|---------|---------|---------------|--------------------------------|

|        |          | 0004<br>0005         | ; Host  | To IOP  | Data Transfer |                                |

|        | (00CE)   | 0006                 | IBASE   | EQU     | 0CEh          | ;IOP Base Address.             |

|        | (00CE)   | 0007                 | STATUS  | EQU     | IBASE+00h     | ;Status Register.              |

|        | (00CF)   | 8000                 | INDATA  | EQU     | IBASE+01h     | ;Input Data Register.          |

|        | (0007)   | 0009                 | IDE     | EQU     | 7             | ;Input Data Empty bit D7.      |

|        | (07.00)  | 0010                 |         | 000     | 7.001         | - Charles of CDOS was a series |

|        | (0100)   | 0011<br>0012         |         | ORG     | 100h          | ;Start of CDOS user area.      |

|        |          | 0012                 |         |         |               | _                              |

|        |          | 0013                 |         | ,       |               | -                              |

| 0100   | 211401   | 0015                 | HOST1:  | LD      | HL, HBUFFO    | Point to host buffer.          |

|        |          | 0016                 |         |         | ,             |                                |

| 0103   | DBCE     | 0017                 | IDE?:   | IN      | A, (STATUS)   | ;Loop until bit Input          |

| 0105   | CB7F     | 0018                 |         | BIT     | IDE,A         | ;Data Empty is set             |

| 0107   | 28FA     | 0019                 |         | JR      | Z, IDE?       | ;                              |

| 0109   | 7E       | 0020<br>0021         |         | LD      | A, (HL)       | then get a buffer character    |

| 010A   | D3CF     | 0021                 |         | OUT     | (INDATA) A    | ;and send to IOP.              |

| 07.077 | 2301     | 0023                 |         | 001     | ( ******      | , and boile to lot "           |

| 010C   | FE24     | 0024                 |         | CP      | 1\$1          | ;Was the character a '\$'      |

| 010E   | 2803     | 0025                 |         | JR      | Z, DONE       | ;delimiter? Exit if so,        |

|        |          | 0026                 |         |         |               |                                |

| 0110   | 23       | 0027                 |         | INC     | HL            | otherwise loop back and        |

| 0111   | 18F0     | 0028                 |         | JR      | IDE?          | ;send the next character.      |

| 0113   | 76       | 0029<br>0030         | DONE:   | HALT    |               |                                |

| 0112   | /6       | 0030                 | DOME:   | UMLI    |               | <i>;</i>                       |

|        |          | 0032                 |         | ;====== |               | =                              |

|        |          | 0033                 |         | •       |               |                                |

| 0114   | 61626331 | 0034                 | HBUFF0: | DB      | 'abc123\$'    | ;Host buffer data.             |

|        |          | 0035                 |         |         |               |                                |

| 011B   | (0100)   | 0036                 |         | END     | HOST1         |                                |

|      |                                         | 0001<br>0002 | ;       | IOP PRO | GRAM 1        |                                 |

|------|-----------------------------------------|--------------|---------|---------|---------------|---------------------------------|

|      |                                         | 0003         |         |         |               |                                 |

|      |                                         | 0004<br>0005 | ; Host  | To IOP  | Data Transfer |                                 |

|      | (0001)                                  | 0005         | INDATA  | EQU     | 01h           | ;Input Data Register.           |

|      | (0001)                                  | 0007         | FLAGS   | EQU     | 02h           | ;Flag Register.                 |

|      | (0002)                                  | 0008         | IDA     | EQU     | 6             | ;Input Data Available bit D6.   |

|      | (0000)                                  | 0009         | IDA     | EQU.    | 0             | , input bata Available bit bo.  |

|      | (4000)                                  | 0010         |         | ORG     | 4000h         | ;Start of IOP RAM memory.       |

|      | (4000)                                  | 0011         |         | ONG     | 400011        | , Beart of for RAM memory.      |

|      |                                         | 0012         |         |         |               | _                               |

|      |                                         | 0013         |         | ,       |               | <del>-</del>                    |

| 4000 | 211440                                  | 0014         | IOP1:   | LD      | HL, IBUFFO    | ;Point to IOP buffer.           |

| 3000 | *************************************** | 0015         | TOET    | מנו     | HM, IBOLL 0   | , roint to for burier.          |

| 4003 | DB02                                    | 0016         | IDA?:   | IN      | A, (FLAGS)    | ;Loop until bit Input           |

| 4005 | CB77                                    | 0017         | TDI     | BIT     | IDA,A         | Data Available is set           |

| 4007 | 28FA                                    | 0018         |         | JR      | Z, IDA?       | ;                               |

| *007 | ZULK                                    | 0019         |         | O.K     | a, iba:       |                                 |

| 4009 | DB01                                    | 0020         |         | IN      | A, (INDATA)   | then get a character from       |

| 400B | 77                                      | 0021         |         | LD      | (HL) A        | the host and stash in buffer.   |

| 400B | "                                       | 0022         |         | میں     | (HL) FA       | , the host and stash in buller. |

| 400C | FE24                                    | 0023         |         | CP      | 151           | ;Was the character a '\$'       |

| 400E | 2803                                    | 0024         |         | JR      | z, done       | delimiter? Exit if so,          |

|      |                                         | 0025         |         |         | -,            | ,                               |

| 4010 | 23                                      | 0026         |         | INC     | HL            | otherwise loop back to get      |

| 4011 | 18F0                                    | 0027         |         | JR      | IDA?          | ;and store another character.   |

|      |                                         | 0028         |         |         |               | ,                               |

| 4013 | 76                                      | 0029         | DONE:   | HALT    |               | i                               |

|      |                                         | 0030         |         |         |               | •                               |

|      |                                         | 0031         |         | :====== |               | =                               |

|      |                                         | 0032         |         | •       | •             |                                 |

| 4014 | (0100)                                  | 0033         | IBUFF0: | DS      | 100h          | ;IOP buffer data.               |

|      | · •                                     | 0034         |         |         |               | •                               |

| 4114 | (4000)                                  | 0035         |         | END     | IOPl          |                                 |

DATA: HOST <- IOP

| IN Ibase → 00h                                    | HOST IN Ibase + 01h                   |

|---------------------------------------------------|---------------------------------------|

| STATUS REGISTER                                   | OUTPUT DATA                           |

| D7 D6 Output Data Available D5 D4 0 D2 D1 D0      | D5 D4 Host Reads D3 D4 D2 D1 D0       |

| IN 02h                                            | IOP OUT 01h                           |

| OUTPUT DATA                                       | FLAG REGISTER                         |

| D7 D6 D5 D4 IOP Writes Data To This Port D2 D1 D0 | D7 Output Data Empty D6 D5 D4 D3 D2 J |

Figure 20: IOP DATA TO HOST

Figure 20 shows the IOP register bits used to transfer data from the IOP back to the host. Again two program segments appear below, one residing in host memory and the other in IOP memory. The IOP program sends the contents of RAM buffer IBUFF1 to the host by polling Flag Register bit Output Data Empty until set, then outputting a single character to register Output Data, then polling bit Output Data Empty again, sending another character, and so on. The host program receives each character by polling Status Register bit Output Data Available until set, then inputting a single character from register Output Data, then polling bit Output Data Available again, reading another character, and so on. Each character read by the host is stored sequentially in host RAM buffer HBUFF1.

CROMEMCO Z80 Macro Assembler version 03.07

|      |        | 0001<br>0002<br>0003 | ;       | HOST PRO  | OGRAM 2       |                                |

|------|--------|----------------------|---------|-----------|---------------|--------------------------------|

|      |        | 0004                 | ; IOP 7 | ro Host 1 | Data Transfer |                                |

|      | (00CE) | 0006                 | IBASE   | EQU       | 0CEh          | ;IOP Base Address.             |

|      | (00CE) | 0007                 | STATUS  | EQU       | IBASE+00h     | ;Status Register.              |

|      | (00CF) | 8000                 | OUTDATA | EQU       | IBASE+01h     | Output Data Register.          |

|      | (0006) | 0009                 | ODA     | EQU       | 6             | ;Output Data Available bit D6. |

|      |        | 0010                 |         |           |               |                                |

|      | (0100) | 0011                 |         | ORG       | 100h          | ;Start of CDOS user area.      |

|      |        | 0012                 |         |           |               | •                              |

|      |        | 0013                 |         | ;======   |               | 2                              |

|      |        | 0014                 |         | •         |               |                                |

| 0100 | 211401 | 0015                 | HOST2:  | LD        | HL, HBUFFl    | ;Point to host buffer.         |

|      |        | 0016                 |         |           |               |                                |

| 0103 | DBCE   | 0017                 | ODA?:   | IN        | A, (STATUS)   | ;Loop until bit Output         |

| 0105 | CB77   | 0018                 |         | BIT       | ODA, A        | ;Data Available is set         |

| 0107 | 28FA   | 0019                 |         | JR        | Z,ODA?        | ;                              |

|      |        | 0020                 |         |           |               |                                |

| 0109 | DBCF   | 0021                 |         | IN        | A, (OUTDATA)  | then get a character from      |

| 010B | 77     | 0022                 |         | LD        | (HL),A        | the IOP and stash in buffer.   |

|      |        | 0023                 |         |           |               |                                |

| 010C | FE24   | 0024                 |         | CP        | '\$'          | ';Was the character a '\$'     |

| 010E | 2803   | 0025                 |         | JR        | Z,DONE        | delimiter? Exit if so,         |

|      |        | 0026                 |         |           |               |                                |

| 0110 | 23     | 0027                 |         | INC       | HL            | otherwise loop back to get     |

| 0111 | 18F0   | 0028                 |         | JR        | ODA?          | ;and store another character.  |

|      |        | 0029                 |         |           |               |                                |

| 0113 | 76     | 0030                 | DONE:   | HALT      |               | 9                              |

|      |        | 0031                 |         |           |               |                                |

|      |        | 0032                 |         | ;======   |               | =                              |

|      |        | 0033                 |         |           |               |                                |

| 0114 | (0100) | 0034                 | HBUFF1: | DS        | 100h          | ;Host buffer data.             |

|      |        | 0035                 |         |           |               |                                |

| 0214 | (0100) | 0036                 |         | END       | HOST2         |                                |

```

0001

0002

IOP PROGRAM 2

î

0003

0004

IOP to Host Data Transfer

0005

(0001)

0006

OUTDATA EQU

01h

;Output Data Register.

(0002)

0007

FLAGS

EQU

02h

;Flag Register.

(0007)

0008

ODE

EQU

Output Data Empty bit D7.

0009

(4000)

0010

ORG

4000h

;Start of IOP RAM memory.

0011

0012

0013

0014

4000

211440

IOP2:

HL, IBUFF1

;Point to IOP buffer.

LD

0015

0016

0017

0018

4003

DB02

ODE?:

TN

A, (FLAGS)

;Loop until bit Output

4005

BIT

CB7F

ODE, A

;Data Empty is set...

4007

28FA

JR

Z,ODE?

0019

4009

0020

7 E

A,(HL)

LD

;then get a buffer character

400A

D301

0021

OUT

(OUTDATA),A

; and send to host.

0022

;Was the character a '$';delimiter? Exit if so,

400C

FE24

0023

CP

151

400E

2803

0024

JR

Z, DONE

0025

4010

23

0026

INC

;otherwise loop back and

4011

18F0

0027

ODE?

; send the next character.

JR

0028

4013 76

0029

DONE:

0030

0031

0032

4014 61626331

0033

IBUFF1: DB

'abc123$'

;IOP buffer data.

0034

401B (4000)

0035

END

IOP2

```

COMMANDS: HOST -> IOP

Figure 21: HOST COMMANDS TO IOP

The host passes commands to the IOP in much the same way that it writes data to the IOP; the main difference between the two is that bit Command Register Empty is IOP software controlled (the bit is not reset when the IOP reads the Command Register -- see Appendix A). Command interpretation is completely software defined. In the program segments which follow, host command byte 00h causes the IOP to reset its Control Register bit Enable S-100 Interrupt Requests (a task the host CPU cannot directly accomplish itself), and command byte OFFh causes the IOP to set the same bit. Any other command byte is considered a null operation by the IOP program.

|      |                                                | 0001<br>0002<br>0003<br>0004         | ;                                         | HOST PR    | OGRAM 3                             | •                                                                                                                                |

|------|------------------------------------------------|--------------------------------------|-------------------------------------------|------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|      |                                                | 0005                                 | , nosc                                    | 10 101     | COmmuna realister                   |                                                                                                                                  |

|      | (00CE)<br>(00CE)<br>(00CE)<br>(0001)<br>(0000) | 0006<br>0007<br>0008<br>0009<br>0010 | IBASE<br>STATUS<br>COMMAND<br>CRE<br>COMO | EQU<br>EQU | OCEh<br>IBASE+OOh<br>IBASE+OOh<br>1 | ;IOP Base Address.<br>;Status Register.<br>;Command Register.<br>;Command Register Empty bit Dl.<br>;Disable Interrupts Command. |

|      | (00FF)                                         | 0011<br>0012                         | COM1                                      | EQU        | 0FFh                                | ;Enable Interrupts Command.                                                                                                      |

|      | (0100)                                         | 0012<br>0013<br>0014                 |                                           | ORG        | 100h                                | ;Start of CDOS user area.                                                                                                        |

|      |                                                | 0015                                 |                                           | ;=====     |                                     | <b>■</b>                                                                                                                         |

|      |                                                | 0016                                 |                                           |            |                                     | New                                                                                                                              |

| 0100 | 310010                                         | 0017                                 | HOST3:                                    | LD         | SP,1000h                            | ;Locate stack.                                                                                                                   |

| 0103 | CD1201                                         | 0018<br>0019                         |                                           | CALL       | CRE?                                | ;Send command to disable                                                                                                         |

| 0106 | 3E00                                           | 0020                                 |                                           | LD         | A,COMO                              | ;S-100 interrupts when bit                                                                                                       |

| 0108 | D3CE                                           | 0021<br>0022                         |                                           | OUT        | (COMMAND),A                         | Command Register Empty is set,                                                                                                   |

| 010A | CD1201                                         | 0022                                 |                                           | CALL       | CRE?                                | ;then send command to enable                                                                                                     |

| 010D | 3EFF                                           | 0024                                 |                                           | LD         | A, COM1                             | ;S-100 interrupts when bit Command                                                                                               |

| 010F | D3CE                                           | 0025<br>0026                         |                                           | OUT        | (COMMAND),A                         | Register Empty is set again.                                                                                                     |

| 0111 | 76                                             | 0027                                 |                                           | HALT       |                                     | ;                                                                                                                                |

|      |                                                | 0028                                 |                                           |            |                                     |                                                                                                                                  |

|      |                                                | 0029                                 |                                           |            | ***                                 | =                                                                                                                                |

|      |                                                | 0030                                 |                                           |            | utine CRE?                          |                                                                                                                                  |

|      |                                                | 0031<br>0032                         |                                           | ;=====     |                                     | <u>=</u>                                                                                                                         |

| 0112 | DBCE                                           | 0033                                 | CRE?:                                     | IN         | A, (STATUS)                         | ;Loop until bit                                                                                                                  |

| 0114 | CB4F                                           | 0034                                 |                                           | BIT        | CRE, A                              | Command Register Empty                                                                                                           |

| 0116 | 28FA                                           | 0035                                 |                                           | JR         | Z,CRE?                              | ;is set,                                                                                                                         |

| 0118 | C9                                             | 0036                                 |                                           | RET        |                                     | ; then return.                                                                                                                   |

|      |                                                | 0037<br>0038                         |                                           |            |                                     | _                                                                                                                                |

|      |                                                | 0038                                 |                                           | ,          |                                     | <del>.</del>                                                                                                                     |

| 0119 | (0100)                                         | 0040                                 |                                           | END        | HOST3                               |                                                                                                                                  |

|      | •                                              |                                      |                                           |            |                                     |                                                                                                                                  |

|      |        | 0001 |         |         |                  |                                    |

|------|--------|------|---------|---------|------------------|------------------------------------|

|      |        | 0002 | ;       | IOP PRO | GRAM 3           |                                    |

|      |        | 0003 |         |         |                  |                                    |

|      |        | 0004 | ; Host  | To IOP  | Command Transfer |                                    |

|      |        | 0005 |         |         |                  |                                    |

|      | (0000) | 0006 | COMMAND |         | 00h              | ;Command Register.                 |

|      | (0000) | 0007 | STATUS  | EQU     | 00h              | ;Status Register.                  |

|      | (0002) | 0008 | CONTROL |         | 02h              | ;Control Register.                 |

|      | (0002) | 0009 | FLAGS   | EQU     | 02h              | ;Flag Register.                    |

|      | (0000) | 0010 | CRA     | EQU     | 0                | Command Register Available bit D0. |

|      | (0000) | 0011 | COM0    | EQU     | 00h              | ;Disable Interrupts Command.       |

|      | (00FF) | 0012 | COM1    | EQU     | OFFh             | ;Enable Interrupts Command.        |