# THE BIG Z REVISION C

2 MHz OR 4 MHz SWITCHABLE Z-80 CPU WITH ON-BOARD SERIAL I/O PORT

# INTRODUCTION

The **JADE BIG Z** Z80 Microprocessor CPU board is a very stable and powerful CPU, designed for the S-100 bus and in reasonable conformity with the proposed IEEE S-100 Bus Standard.

The **Big Z** CPU provides on-board EPROM and on-board serial communications via an RS232C standard interface which supports transmit and receive data and one standard handshake line.

The **Big Z** CPU board has been manufactured to the most exacting specifications, using the highest quality material and components conservatively rated for long life. As such, it may be expected to give you many thousands of hours of useful active service.

If you have purchased the **Big Z** as an assembled and tested unit, you should know that it has passed rigorous tests, running in a real-time disk-based

environment and executing the most complicated programs we can devise. Before it goes out the door, every assembled and tested **Big Z** must prove itself to our picky engineering personnel.

Although any component can fail, most ICs die in their infancy, and the burn-in time each **Big Z** receives insures that we catch practically all of these infant mortalities.

If you have purchased the **Big Z** as a kit, we strongly urge you to read this manual in its entirety before attempting to construct the board. Although there are about as many ways of assembling a board as the tenth power of the components on it, if you will follow the assembly instructions step-by-step, construction will be easier for you and much more pleasurable for both of us.

# **FEATURES**

On-board 2708/2716/2732 EPROM can be addressed to any 1K, 2K, or 4K boundary. \* Power-on jump directly to the on-board EPROM. \* Optional wait state for on-board EPROM. \* On-board EPROM may be used in shadow mode (accessed only after power-on or reset). \* Allows full 64K RAM memory to be used. \* On-board 8251 USART for synchronous or asynchronous RS232 operation. \* Independent crystal-controlled baud rate generator provides all standard baud rates from 110 to 9600. \* Switchselectable 2 or 4 MHz operation. \* Optional M1 wait states can be generated. \* Automatic MWRT generation if a front panel is not used, automatically disabled if a front panel is connected. \* DMA capability. \* Latched data output bus provides additional data hold time for reliable operation with all

device types. \* Straight-through address and data paths provide improved read access times for I/O and memory devices. \* On-board serial port switchselectable to any pair of I/O port locations from 00 through FE hex. \* Reverse channel capability on USART allows use with buffered peripherals or devices with "not ready" indication. \* Front panel data cable interface. \* Fully buffered S-100 interface. \* Separate voltage regulators (no diodes) assure a clean, stable power supply. \* Intelligent, clean layout of PC board. \* Reflow soldered, plated, and fully masked PC board. \* Gold-plated S-100 bus connector is Imsai standard. \* Complete 1K monitor software listing included in manual. \* Fully warranted by JADE, one of the largest microcomputer product suppliers in the world.

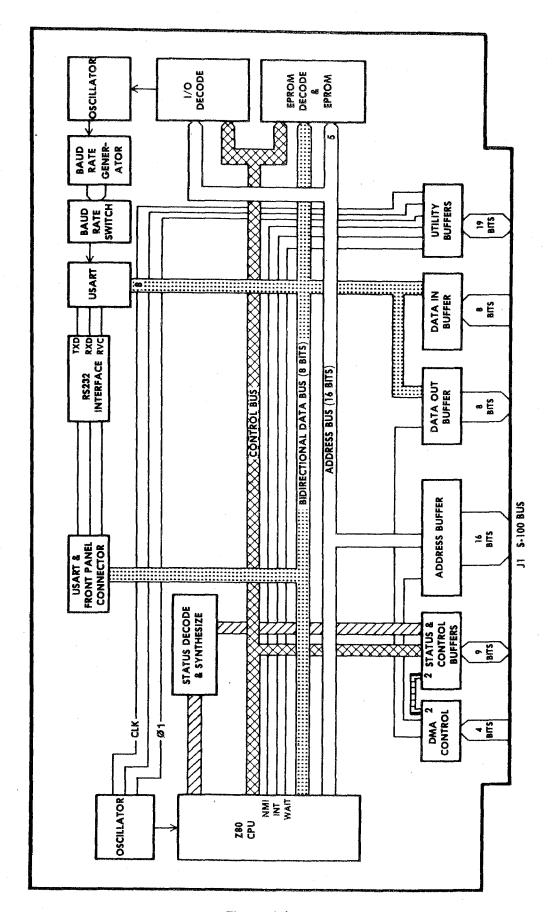

### **FUNCTIONAL DESCRIPTION**

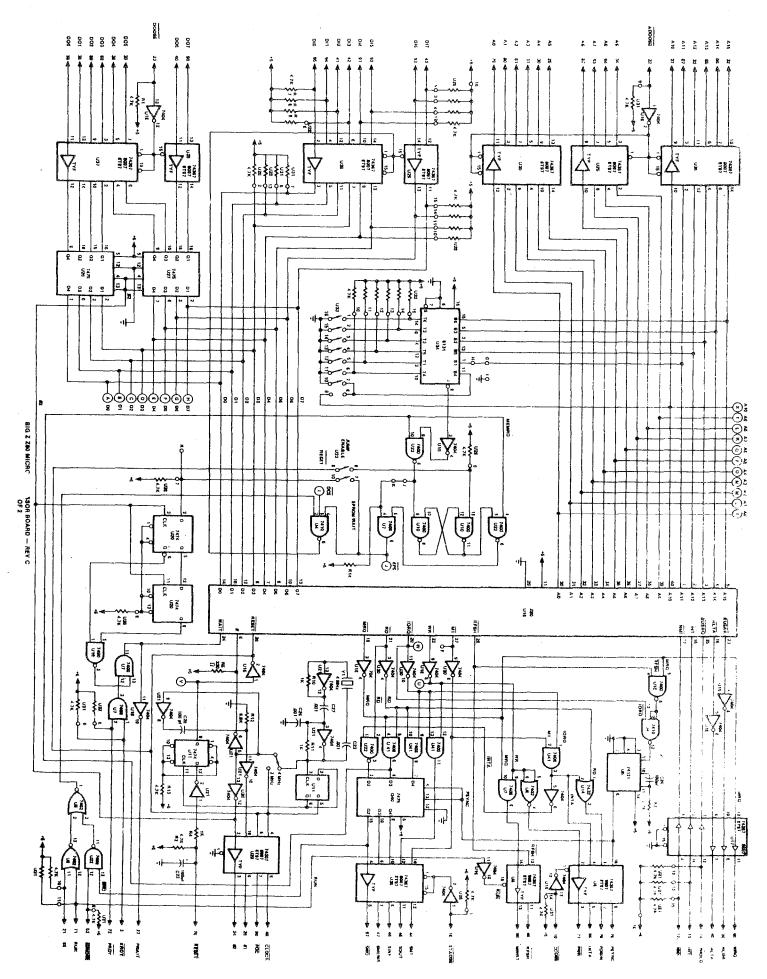

Figure 1-1 is a block diagram describing the functional blocks contained on the **JADE Big Z** CPU. The following sections describe each of the blocks in Figure 1-1.

#### Z80 CPU

At the heart of the Big Z is the powerful Z80 microprocessor which provides the major control signals required to read and write to memory and I/O ports. Also generated by the Z80 are a 16-bit address bus and an 8-bit bidirectional data bus.

#### **OSCILLATOR**

The oscillator is a crystal-controlled circuit which generates Phi1 and Phi2 clock signals for the S-100 bus, the Clock\* S-100 signal, and the internal system clock. Also involved with this circuitry are the Reset and Power-on Clear signals.

#### STATUS AND CONTROL BUFFERS

The status and control buffers provide the drive for the various S-100 bus status and control signals. During a DMA operation (when BUSAK is high on the Z80 chip), or during maintenance functions, the status and control buffers are tri-stated, allowing a DMA device to control the bus as a temporary bus master.

#### ADDRESS BUFFER

The address buffer is a 16-bit tri-state buffer which drives the 16-bit address to the S-100 bus. It also is tri-stated during DMA operations or maintenance functions.

### DATA OUT BUFFER

The data out buffer is an 8-bit tri-state buffer which drives the 8 data out signals to the S-100 bus. Data is gated out to the S-100 bus only during memory write or I/O output cycles. The data out buffer is tri-stated during DMA operations or maintenance functions.

#### DATA IN BUFFER

The S-100 data in bus is provided to the Z80 during read memory or I/O input bus cycles by the data in

buffers. These buffers are disabled during write memory or I/O output cycles, and for DMA operations. They may also be disabled by the following conditions;

RUN and SS (Single Step) low (false) at pins 71 and 21 of the S-100 bus.

On-board EPROM selected during a memory read operation.

USART selected during an I/O operation.

Power-on jump enabled and Power-On Latch (2 sections of U10) is set.

#### MEMORY DECODE AND CONTROL

The memory decode and control circuitry decodes the high-order address bits from the internal address bus and selects the EPROM. This block also generates the signals required to disable the data in buffers and interacts with the Shadow option circuitry to phantom out the EPROM.

#### **EPROM**

The on-board EPROM can be either a 1K (2708-type), 2K (2716 or TMS2716 type), or 4K (2732-type) EPROM. The EPROM may be switch selected for any 1K, 2K, or 4K boundary, depending on the type of EPROM installed.

#### I/O ADDRESS DECODE AND CONTROL

The I/O address decode and control circuitry decodes the lower 8 bits of the internal address bus to determine which ports are being accessed during I/O instructions. This block also interacts with the EPROM select circuitry and the circuitry which disables the data in buffers.

#### SERIAL I/O

The serial I/O provides synchronous and asynchronous communications via RS232C level interfaces. Included in this block is the crystal-controlled oscillator and baud rate generator for the 8251 USART.

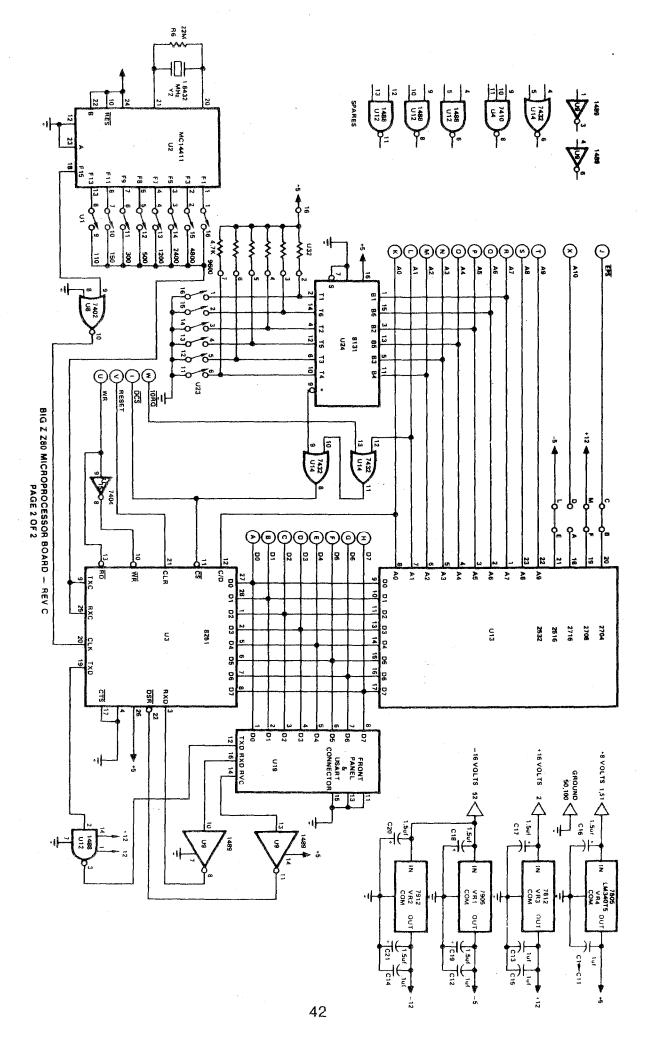

Figure 1.1

#### TECHNICAL DESCRIPTION

#### S-100 INTERFACE

#### Address Bus

The internal address bus is driven to the S-100 bus by tri-state buffers U25, U36, and a portion of U35. These buffers (8T97, 8097, or 74367 ICs) are tri-stated during DMA operations or maintenance functions. This is accomplished via one of the inverter sections of U18, which is driven by the ADDSB\* signal on pin 22 of the S-100 bus. Normally, the input to the inverter is held high by a pullup resistor on pin 1 of U18, which forces a low output from the inverter on pin 2. This low level signal is routed to the enable pins on the address buffers.

When ADDSB\* goes true (low), the output on pin 23 of the inverter U18 goes high, disabling the address buffers.

#### Data In Bus

The internal bidirectional data bus is driven from the S-100 bus by tri-state buffers U38 and a portion of U29. These buffers are enabled only during read memory or I/O input cycles. They are also disabled by the following conditions:

- 1. SSWDSB\* is low (true) at pin 53 of the S-100 bus. This signal is one of the inputs to NAND gate U22, along with sWO\*. It is normally held high (false) by pullup resistor pack U31.

- 2. RUN or SS on pins 71 and 21 respectively of the S-100 bus is low (false). These signals are held normally high by pullup resistors in resistor pack U31. They are inputs to NOR gate U8. This NOR output is NORed with the NAND of SSWDSB\* and sWO\* by another section of U8, and this signal is applied to pin 3 of the 3-input NAND gate U4, where it is NANDed with the signals discussed below.

- 3. On-board EPROM is selected during a memory read operation. The signal EPS\*, which is the output from pin 6 of AND gate U7 is applied to pin 4 of NAND gate U4.

- 4. On-board USART selected during an I/O operation (either input or output cycle). The DCS\* signal, generated as the output of OR gate U14 at pin 8, is applied to pin 5 of NAND gate U4, whose output drives the tri-state input of data in buffers U38 and U29.

- 5. Power-on Jump is enabled and the Power-On Latch (2 sections of U10) is set.

#### **Data Out Bus**

The internal data bus is provided to the S-100 DO (data out) bus for memory write or I/O output cycles by tri-state buffers U37 and a portion of U25. The DODSB\* signal on pin 23 of the S-100 bus will disable these buffers when it goes low (true). It is provided to the tri-state control inputs of the buffers via inverter U18. The input to inverter U18 on pin 13 is held normally high by pullup resistor R1, forcing the output of the inverter to be low, thereby enabling the buffers. When DODSB\* goes true (low), the pullup resistor is overcome and the tri-state inputs of the buffers go high, disabling (tri-stating) these buffers.

The input to the data out buffers are provided by latches U27 and U26. Data is passed through the latches by the high level of Phi2 clock. The falling edge of Phi2 clock disables the latches.

A true (low) signal at DODSB\* will tri-state the data out bus for DMA or maintenance functions.

#### Status Signals

The primary status signals sM1, sOUT, sINP, sMEMR, and sWO\* are provided to the S-100 bus via tri-state buffer U39. U39 is tri-stated by STADSB\*, on pin 18 of the S-100 bus, going low (true). Normally, a pullup resistor holds the input to inverter U30 on pin 1 high, forcing the output of inverter U30 on pin 2 low, enabling the buffer at U39. When STADSB\* goes true (low), the output of the inverter goes high, tri-stating the U39 buffer.

sM1 on pin 44 of the S-100 bus is provided by the CPU through buffer U39 and inverter U30. It is derived from the Z80's M1\* signal, on pin 27 of the CPU. This signal is applied to pin 9 of inverter U30. The output of U30, pin 8, will be high when the Z80 M1\* signal is true (low). The output of U30 is applied to input pin 14 of buffer U39 and is transferred to the S-100 bus from output pin 13 of buffer U39, provided that U39 is not tristated by a true (low) signal on STADSB\*

sM1 signals that the processor is fetching an instruction op code; therefore, it signals an opcode fetch cycle.

sOUT on pin 45 of the S-100 bus is provided by the CPU through buffer U39, AND gate U41, and inverters U18 and U30. It is derived from the Z80 WR\* and IORQ\* signals. These outputs from the Z80, on pins 22 and 20 respectively, are inverted by U18 and U30. The outputs

of these inverters, on pins 8 and 10 respectively of U18 nd U30, will be high when WR\* and IORQ\* are true (low). If both of these outputs are high—meaning that WR\* and IORQ\* are true—the output of AND gate U41, on pin 11, will also be high. This signal is output to pin 12 of U39 and is transferred to the S-100 bus from U39 output pin 11, provided U39 is not tri-stated by STADSB\* being true (low).

sOUT signals an output to an I/O port; therefore, it may be referred to as an I/O output cycle signal.

sINP on pin 46 of the S-100 bus is provided by the CPU through buffer U39, latch U40, AND gate U41, and inverter U30. It is derived from the Z80's RD\* and IORQ\* signals. These outputs from the Z80, on pins 21 and 20 respectively, are applied to U30 inverter pins 3 and 11. The outputs of the inverter, on pins 4 and 10 respectively, are applied to AND gate U41 on input pins 10 and 9. When the outputs of inverter U30 are high (Z80 RD\* and IORQ\* signals are low (true)), the output of AND gate U41, on pin 8, will be high. This signal is applied to the input of U40 latch on pin 7. Now, when PSYNC is high, the signal is clocked through U40, being output on pin 9, and is applied to buffer U39 input pin 10. The signal is transferred through the buffer, output on pin 9, to S-100 bus pin 46, provided U39 is not tri-stated by STADSB\* being true (low):

sINP signals an input from an I/O port; therefore, it may be referred to as an I/O input cycle signal.

sMEMR on pin 47 of the S-100 bus is provided by the CPU through buffer U39, latch U40, AND gate U41, and inverters U18 and U30. It is derived from the Z80's RD\* and MRQ\* signals. These outputs from the Z80, on pins 21 and 19 respectively, are applied to inverters U30 and U18, on input pins 3 and 3 respectively. The output of these inverters, on pins 4 and 4 respectively. will be high when the Z80 signals RD\* and MRQ\* are true (low). The outputs of the inverters are applied to input pins 5 and 4 of AND gate U41. When both of these inputs are high, the output of U41, on pin 6, will be high. This output is applied to input pin 6 of U40, Now. when PSYNC is high, the signal is clocked through the latch and is output on pin 10 of U40. This output is applied to input pin 6 of buffer U39. It passes through the buffer, is output on pin 7, and is applied to S-100 pin 47, provided that STADSB\* is not active (low).

sMEMR signals a read from memory; therefore, it may be referred to as a memory read cycle signal.

sWO\* on pin 97 of the S-100 bus is provided by the CPU through buffer U39, latch U40, NAND gate U22, and inverter U18, together with inverter U30 and AND gate U41. It is derived from the Z80's RD\* and INTA\* signals, where INTA\* is derived—itself—from the Z80 gnals M1\* and IORQ\*.

Z80 signal RD\*, on pin 21 of the CPU, is applied to input pin 2 of NAND gate U22. The other input pin is

driven by the output of inverter U30, pin 6. The input to this inverter is the output of AND gate U41. U41 ANDs IORQ with M1. These signals are provided from the Z80's IORQ\* and M1\* signals on pins 20 and 27 respectively of the CPU.

When RD\* is false (high) and IORQ\* and M1\* are both false (also high), the output of NAND gate U22, pin 3, will go low. This low is applied to latch U40 on pin 3 and is clocked through the latch by PSYNC, being output on U40 pin 15. This output is applied to U39 buffer input pin 4, is transferred through the buffer to pin 5, and output to S-100 bus pin 97 as sWO\*. Note that the following conditions must be met for sWO\* to be true: the processor is not in a read cycle (RD\* is false—high), and neither is it in an Interrupt Acknowledge cycle (IORQ\* ANDed with M1\* is false).

sWO\* signals that the processor is not in a data input cycle. It is used as an early indication that a write operation will take place.

#### Other Status Signals

The IEEE-defined status signal sXTRQ\* is not supported by the Big Z CPU. This signal is used to request a 16-bit wide input or output, and gangs the DO and DI buses together to form a single 16-bit bidirectional data bus. Since the Big Z is not a 16-bit processor, this signal protocol is not implemented.

sINTA on pin 96 of the S-100 bus is provided by the CPU through buffer U6, AND gate U41, and inverter U30. It is derived from the Z80's IORQ\* and M1\* signals. These outputs from the Z80, on pins 20 and 21 respectively, are inverted by inverter U30. The signals are applied to input pins 11 and 9 of U30, and output on pins 10 and 8, respectively, as inverted signals. They are then applied to input pins 1 and 2 of AND gate U41 When the Z80 IORQ\* and M1\* are both true (low), the outputs of both inverters will be high. These high signals, applied to AND gate U41, result in a high being output on pin 3 of U41. This is applied to buffer U6 input pin 4, transferred through the buffer, output on pin 4, and applied to S-100 bus pin 96 as sINTA, provided that CCDSB\* is false (high).

sINTA signals that the processor is acknowledging an interrupt request from a peripheral device; therefore, it may be referred to as an interrupt acknowledge signal.

sHLTA on pin 48 of the S-100 bus is provided by the CPU through buffer U17 and inverter U18. It is derived from the Z80's HLTA\* signal on pin 18 of the CPU. HLTA\* is applied to pin 5 of inverter U18, where it is inverted and output on pin 6 as HLTA. HLTA is applied to buffer U17, input pin 6, is transferred through the buffer, and output on pin 7, where it is applied to S-100 bus pin 48. Buffer U17 is always enabled, since the tristate inputs are grounded.

#### Control Signals—Output

There are five control signals defined by IEEE as control outputs. These are: pSYNC, pSTVAL\*, pDBIN, pWR\* and pHLDA.

pSTVAL\* is not implemented on the Big Z CPU. This is defined as a signal which, in conjunction with pSYNC, indicates that stable address and status information may be sampled from the bus in the current cycle. For Big Z applications, it is redundant and is therefore not implemented.

pSYNC is generated by one-shot U5, which is clocked by the Z80 signals IORQ\*, RFS\* and MRQ\*. pSYNC is transferred to pin 76 of the S-100 bus through buffer U6, which may be tri-stated by the signal CCDSB\*.

Z80 RFSH\* is applied directly to pin 4 of NAND gate U10, where is is NANDed with MRQ. MRQ is derived from the Z80 MRQ\* through inverter U18. MRQ\*, on pin 19 of the CPU, is applied to U18 pin 3, inverted, and output on pin 4 as MRQ. MRQ is applied to input pin 5 of NAND gate U10. When the Z80 signal MRQ\* is true (low), and RFSH\* is false (high), both inputs of the NAND gate U10 will be high, resulting in a low output from pin 6. This output is NANDed by gate U4 with IORQ\* from the Z80 pin 20. The output of U4 at pin 12 is applied to one-shot U5. The multivibrator clocks out, with its timeout period being determined by C24, a 100 picofarad capacitor, and R2, a 2.7K ohm resistor. The timeout, with these values, is approximately 270 nanoseconds. The output of the U5 multivibrator, on pin 6, is applied to U6 buffer input pin 10. It is transferred through U6 to output pin 9, and from there to the S-100 bus pin 76 as pSYNC.

pSYNC is only high during the first part of a memory or I/O cycle due to the effect of multivibrator U5. It is used to indicate the start of a new bus cycle, and is provided for those S-100 devices that look at status information during this time as per 8080 device conventions.

pDBIN on pin 78 of the S-100 bus is provided by the CPU through buffer U6 as an OR of Z80 signals RD\* and IORQ\* being—either of them—true. Z80 signal RD\*, on pin 21 of the CPU, is inverted by inverter U30. The output of U30 on pin 4 is applied to input pin 1 of OR gate U14. The other input to this OR gate, pin 2, is derived from the output of AND gate U41, which ANDs together IORQ\* and M1\* both true to generate INTA (Interrupt Acknowledge). Either INTA or RD\* true will generate a high output from OR gate U14, pin 3. This is applied to U6 buffer input pin 6, transferred through the buffer to output pin 7, and drives S-100 bus pin 78 (pDBIN), provided that the buffer is not tri-stated by a true condition of CCDSB\*.

pDBIN signals that the processor is in a data input

cycle, either I/O or memory read, therefore, it is a generalized read strobe gating data from an addressed bus slave onto the data in bus.

pWR\* on pin 77 of the S-100 bus is provided by the CPU through buffer U6 as a slightly delayed WR\* signal from the Z80 CPU. Z80 signal WR\*, on pin 22 of the CPU, is applied to inverter U18. The output of U18 on pin 8 is applied to both inputs of OR gate U8 on pins 5 and 6. The output of this OR gate on pin 4 is applied to buffer U6 input pin 2, is transferred through the buffer to output pin 3, where it is driven to S-100 bus pin 77, provided that buffer U6 is not tri-stated by CCDSB\* being true.

pWR\* signals that the processor is in a data output cycle, either I/O or memory; therefore, it is a generalized write strobe that writes data from the bus into an addressed bus slave.

pHLDA on pin 26 of the S-100 bus is provided by the CPU through buffer U17. It is simply an inverted Z80 BUSAK\*. BUSAK\* from the Z80, on pin 23, is applied to inverter U15 pin 5. The output of this inverter is applied to buffer U17 input pin 10, is transferred through the buffer, exits on pin 9, and is then applied to S-100 bus pin 26. When BUSAK\* is true (low) on the Z80, pHLDA will be high on the S-100 bus.

pHLDA is the hold acknowledge signal that indicates to the highest priority device that is requesting a hold that the CPU is relinquishing control of the bus. When a device requests a hold and is acknowledged by the CPU, the Z80 tri-states its own data and address busses and generates BUSAK\* true, which is passed to the S-100 bus as pHLDA. This signal is always passed onto the bus, since the tri-state inputs of buffer U17 are grounded and the buffer is always enabled.

#### Control Signals—Input

There are six control input lines defined by IEEE. These are: RDY, XRDY, INT\*, NMI\*, HOLD\*, and SIXTN\*.

SUXTN\* is not implemented on the Big Z CPU. SIXTN\* is a 16-bit acknowledge signal indicating that a requested 16-bit data transfer is possible. Since the Big Z is an 8-bit oriented CPU, this signal is not required.

RDY is provided to the CPU from S-100 bus pin 72. This is a general ready line, and is specified as an open collector line. It is input to the CPU card from S-100 connector pin 72 and is routed to AND gate U7 where it is ANDed with XRDY. A pullup resistor on resistor pack U32 holds pin 2 of AND gate U7 normally high.

XRDY is provided to the CPU from S-100 bus pin 72. This is a special ready line commonly used by front panel devices to stop and single-step the processor. The IEEE does not specify it is an open collector line.

therefore it should not be used by other cards on the bus else a bus conflict may be created. XRDY is also routed to AND gate U7. A pullup resistor on resistor pack U31 holds pin 1 of AND gate U7 normally high.

A low on either input of U7 will result in a low output from pin 3. In other words, when either XRDY or RDY go false (low), the output of U7 will go low. The output of U7 (pin 3) is applied to input pin 12 of AND gate U7, where it is ANDed with the output of the wait-state generator U20, which is normally low unless a wait state is being generated. The output of U7, pin 11, is applied to the Z80 WAIT\* input on pin 24 of the CPU. Therefore, a wait state is generated to the Z80 by either the wait state generator U20, or by XRDY or RDY being pulled low (going false) on the S-100 bus.

INT\* and NMI\* are input directly to the corresponding pins on the Z80 (pins 16 and 17, respectively), through input buffer U17. The tri-state inputs of U17 are grounded; therefore, the buffer is always enabled and these signals pass unimpeded through the buffer to the Z80 CPU.

These two lines are used to request service from the CPU. The INT\* line may be masked by a Disable Interrupt command to the CPU, but the NMI\* line is non-maskable and will always be responded to by the Z80. Both lines should be asserted as a level, rather than a pulse, and should be held true until the interrupt is acknowledged.

HOLD\* is input to the CPU from S-100 bus pin 74, through buffer U17. The output of U17, pin 3, is routed directly to the BUSRQ\* line on the Z80 CPU on pin 25. Buffer U17 is never tri-stated, since its tri-state inputs are grounded; therefore, the CPU will always respond to HOLD\*.

HOLD\* is specified as an open collector line and signals that a bus device is requesting the Z80 to relinquish the bus for a DMA operation.

HOLD\*, NMI\*, and INT\* are held normally high byu resistor pack U31 on the inputs of buffer U17.

#### **Non-IEEE Control Lines**

RFSH\* is provided to the S-100 bus as the non-inverted RFSH\* signal of the Z80 CPU. Z80 RFSH\* on pin 28 of the CPU is routed to input pin 12 of buffer U6. It is transferred through the buffer, exits on pin 11, and is routed to S-100 bus pin 66. This signal is generated as a service to dynamic memory cards that utilize the Z80 RFSH\* signal.

MRQ is provided to the S-100 bus as the inverted MRQ\* signal of the Z80 CPU. Z80 MRQ\*, on pin 19 of the CPU, is inverted by U18, and is applied to input pin 12 of buffer U17 as MRQ. It is transferred through the buffer, exits on output pin 11, and is routed to S-100 bus pin 65. This signal is generated as a service to memory and other cards that require the MRQ signal.

Both of the above signals utilize S-100 pins that have not been defined by the IEEE S-100 Standards Committee; therefore, there should be no conflict with IEEE S-100 standard cards.

pWAIT is provided to the S-100 bus as the inverted WAIT\* signal going into pin 24 of the Z80 CPU. It is buffered by inverter U18, and is generated as a service to those cards that may require it. It, also, uses an IEEE undefined S-100 pin, pin 27.

#### **DMA Control Lines**

The primary DMA control lines utilized by the Big Z CPU card are: DODSB\*, ADDSB\*, STDSB\*, and CCDSB\*.

DODSB\* comes into the Big Z CPU via pin 23 of the S-100 bus. It is routed through inverter U18, and is applied to the tri-state inputs of U37 and that portion of U25 which is concerned with the Data Out bus. The input side of inverter U18 is held normally high by pullup resistor R1. When DODSB\* becomes true (low), the output of inverter U18 becomes high, disabling the data out buffers.

ADDSB\* comes into the Big Z CPU via pin 22 of the S-100 bus. It is routed through inverter U18 (pins 1 and 2), and is applied to the tri-state inputs of U36, U35, and that portion of U25 which is concerned with the Address bus. The input side of inverter U18 is held normally high by a pullup resistor in resistor pack U31. When ADDSB\* goes true (low), the output of inverter U18 will go high, disabling the address bus buffers

STADSB\* comes into the Big Z CPU via pin 18 of the S-100 bus. It is routed through inverter U30, and is applied to the tri-state inputs of U39. The input side of inverter U30 is held normally high by a pullup resistor in resistor pack U28. When STDSB\* becomes true (low), the output of inverter U15 goes high and disables buffer U6, tri-stating pSYNC, pDBIN, sINTA, and pWR\*

The DMA arbitration lines DMA0\* through DMA7\* are not implemented on the Big Z CPU.

#### SYSTEM UTILITIES

#### **System Power Lines**

- 1. A positive 8 volt DC supply is assumed on S-100 pins 1 and 51. This supply is routed to voltage regulator VR4 where it is regulated to the plus 5 volts required by the chips on the board. A 1.5 microfarad tantalum capacitor is located on the input side of VR4, and a 0.1 microfarad ceramic capacitor is located at various places on the board, serving to bypass transients and helping to keep the plus 5 volt supply steady.

- 2. A negative 16 volt supply is assumed on S-100 bus pin 52. This supply is routed to voltage regulators VR1 and VR2, where it is regulated to the minus 12 volts and minus 5 volts required by the chips on the board. A

1.5 microfarad tantalum capacitor is located on both sides of both regulators, which serve to keep the voltage supply steady.

- 3. A positive 16 volt supply is assumed on S-100 bus pin 2. This supply is routed to VR3 where it is regulated to the plus 12 volts required by the chips on the board. In common with VR4, a 1.5 microfarad tantalum cap is located on the input side of VR3, and a 0.1 microfarad cap is located on the output side.

- 4. Ground lines are assumed on pins 50 and 100 of the S-100 bus. The Big Z CPU does not implement the ground lines on pins 20, 53, and 70 specified by the IEEE S-100 standard.

#### System Clock

The system clock, referred to on-board the Big Z CPU as Phi2, is generated by the Big Z oscillator section and is output to the S-100 bus on pin 24 through buffer U29.

Phi1 is also generated by the Big Z oscillator section and is output to the S-100 bus on pin 25 through buffer U29. **CAUTION:** Phi1 conflicts with the IEEE pSTVAL\* signal line. In an IEEE system, this line must be cut. It is provided as a service to those cards that may require it. If no cards in your system require the Phi1 clock line, we suggest that this line should be cut.

The primary system clock is the Phi2 clock, which provides the control timing for all bus cycles.

CLOCK is derived from the Big Z oscillator section and is routed to the S-100 bus on pin 49, through buffer U29. It is a 2 MHz signal, regardless of the optional switch settings which select an internal 2 or 4 MHz clock. IEEE specifies a 2 MHz clock signal on this pin.

# System Reset Functions

RESET\*. When RESET\*, coming into the Big Z CPU from S-100 bus pin 75, goes low (true), U11 provides a RESET\* signal to the Z80 CPU, and to the Power-On Latch. This signal is also provided to the S-100 bus as POC\* (Power-On Clear\*) on S-100 pin 99. RESET\* and POC\* are held low for approximately 470 milliseconds due to the time it takes to recharge C22, a 100 microfarad electrolytic capacitor, through R3, a 4.7K ohm resistor. This meets the IEEE specification of a minimum active period of 10 milliseconds for POC\*

#### **Memory Write Strobe**

MWRT is provided to the S-100 bus on pin 68 via buffer U6. It is derived from the Z80 signals MRQ\* and WR\* true (active low on pins 19 and 22 of the Z80 chip), ANDed together by AND gate U17. When WR\* and MRQ\* on the Z80 are true, both inputs to AND gate U7 will be high, since the Z80 signals are inverted by inverter U18.

The generation of MWRT is inhibited when a front panel is connected to the system, and the front panel is

allowed to generate its own MWRT signal.

#### **Special Caution**

SSWDSB\* is provided to the Big Z CPU on S-100 bus pin 53. This signal is used as a sense-switch disable line on Imsai and other front panels. It is in direct conflict with IEEE S-100 standards, which define pin 53 as a ground line. If the Big Z CPU card is to be used with an IEEE S-100 system, or in an IEEE-standard motherboard, such as the JADE ISO-BUS, this line must be cut between pin 12 of NAND gate U22 and pin 53 of the S-100 bus. Since it is held normally high by the pullup resistor in resistor pack U31, cutting this line will not affect the normal operation of the CPU—it will merely allow it to run.

This concludes the Technical Description of the Big Z/S-100 interface. The following sections are a Technical Description of the EPROM interface, the USART interface, and the Oscillator sections of the board.

#### **EPROM INTERFACE**

The EPROM interface circuitry is comprised of DM8131 comparator U34, switch module U33, NAND gates U10, U22, and U4, inverter U15, and AND gate U7.

The comparator at U34 monitors the state of address lines A10 through A15 (depending on which EPROM you have selected) on the internal address bus. It compares the state of these lines to the settings of switch module U33. If a particular switch (1 through 7) of U33 is closed, the switch-side inputs to comparator U34 are grounded (low). If the switches are open, the switch-side inputs to comparator U34 are pulled high by pullup resistors in resistor pack U32.

When a state of equality exists between the switch settings and the current state of A10 through A15, the equal compare output at pin 9 of U34 will go low. This signal is always inverted by inverter U15; therefore, when the comparator finds equality, the output of U15 will be high. Conversely, when there is inequality, the output of U15 will be low.

The output of U15 is applied to input pin 9 of NAND gate U22, where it is NANDed with the output of AND gate U41, pin 6, defined as MEMRD (memory read). When equality is true (high at this point) and MEMRD is true, the output of NAND gate U22, pin 8, will be low; but if either MEMRD or equality is false (low), the output of U22 will be high.

NAND gates comprising two sections of U10 are connected as a flipflop whose SET input is at pin 13, and whose RESET input is at pin 9. This cross-connected set of NAND gates is referred to as the Power-On Jump/Reset Latch (hereafter referred to as the POJ Latch).

The RESET\* signal, connected to RESET\* pin 26 of the Z80 CPU, is connected to the SET input of the POJ latch through switch 8 of switch module U23. When this switch is closed, a negative pulse from the RESET\* line will set the latch. The SET input of the POJ latch is held normally high by a pullup resistor in resistor pack U28.

Consider a power-on sequence: the state of comparator U34 may be indeterminate, but we know that RESET\* will be low (true); therefore, a low pulse will be applied to pin 13 of U10. This results in a high output which is routed to pin 10, forcing pin 8 to go low. Now we have two lows on the inputs of 13 and 12 at U10, so the output on pin 11 will definitely be high. This circles around, like a dog chasing its own tail, reinforcing its own state and tending to keep the flipflop set. This high output is also applied to NAND gate U22 via input pin 5.

Since the first instruction the Z80 will execute is a memory read, MEMRD will also soon go high. This forces the output of NAND gate U22, pin 6, low. This low is applied to AND gate U7, which results in a low being output on pin 6, and the EPROM is selected (EPS\* becomes true). Now the Z80 will begin reading its instructions from the EPROM. This state of affairs will continue until the EPROM jumps outside its own range.

EPS\* can only be generated by one of the following conditions: The POJ latch is set, or there is a state of equality on the comparator and MEMRD is true. The first condition is met during reset; the second condition is met when we are doing memory reads in the address range selected by the switches on U33.

EPS\* is applied to pin 4 of NAND gate U4. If EPS\* is true (low), the output of U4 at pin 6 must be high; therefore, the data in buffers are disabled, and we can only read from the EPROM.

By the same token, if we are *not* reading from the EPROM, EPS\* will be false (high). If we are reading from the USART, DCS\* will be true (low), and again the output of U4 will go high, disabling the data in buffers. If EPS\* is false (high), and DCS\* is also false (high), there is yet another condition that can tri-state the data in buffers: SSWDSB\* is true (low) at pin 53 of the S-100 bus (remember, we told you to cut it when the Big Z was used in a system where pin 53 is always grounded), or either RUN or SS is low (false) at pins 71 and 21 of the S-100 bus.

How does the EPROM get selected in the Shadow Mode? Simple. The address switches on U33 don't necessarily have anything to do with it. When the CPU is reset, the RESET\* line at pin 13 of U10 will go low, forcing the output high and setting the POJ latch. The first instruction executed by the Z80 will be a read (op code fetch), so pin 4 of U22 goes high along with pin 5

(the SET condition of flipflop U10). This outputs a low to pin 5 of U7. The other side of this AND gate is held high by the pullup resistor R14, and since the J-K link is cut, it must remain high, irrespective of the state of the output of U22 pin 8, because there is nothing to pull it low. Therefore, a lot on pin 5 of U7 ANDed with a high on pin four must result in a low being output from pin 6, which is—you guessed it—the EPS\* signal. Since the address bus of the Z80 will be at zero, and we no longer care about the state of A10-A15, the Z80 must begin executing instructions from the EPROM.

Now, when MEMRD is true and we have an equality from the comparator, the POJ latch is reset and the EPROM is deselected, never to be heard from again and vanishing into thin air like a Hindu fakir. Why? Because the only thing that will set the POJ latch again is another reset or power-on condition. Voila! We are Shadowed.

Note that the Z80 can do memory writes to anywhere in memory, and all I/O operations, and even reads from memory as long as the address range from which it is reading is different from that selected by the switches of U33.

This circuitry is subtle, and not immediately apparent—but trust us, it works. A little pencil-and-paper doodling with logic equations will prove it to even the most stubborn doubter.

#### **USART INTERFACE**

The USART interface circuitry is comprised of comparator U24, switch module U23, pullup resistor pack U32, the baud rate generator and its associated crystal, OR gate U14, inverter U15, NOR gate U8, the USART itself (an 8251), and the RS232 level shifters at U12 and U9.

The lower portion of the internal address bus is monitored by the comparator U24 on lines A2-A7. The current state of the address bus is compared to the switch settings on U23 switches 1 through 6. As with the EPROM select circuitry, the switch-side inputs to the comparator can be either low or high—high if the switch is open by courtesy of resistor pack U32, or low by virtue of the fact that when a switch is closed it is grounded.

When equality is found, pin 9 of the comparator will go low. This signal is applied to pin 9 of OR gate U14, where it is ORed with the output of OR gate U14, pin 11. U14's section whose output is on pin 11 ORs A1 with IORQ\*. DCS\* is generated by an IORQ\* true (low) or A1 low, ORed with equality from comparator U24. The output of U14 pin 8 is also applied to U4 pin 5 as DCS\* to disable the data in buffers

Tx and Rx clocks are provided to the USART via the MC14411 baud rate generator, whose internal timing is determined by Y2 crystal. A 16-times maximum baud

rate (9600 baud or 153.6 KHz) is provided by NOR gate U8. One input, pin 8, is grounded; the other is routed in from the baud rate generator U2 pin 18.

The Tx data output from the 8251 USART is sent to pin 2 of U12, an MC1488 RS232 level shifter, where it is output from pin 3 as a level that swings between plus and minus 12 volts.

Similarly, the Rx data input to the USART is sent from RS232 level shifter U9 to pin 3 of the USART, as is the Reverse Channel signal. Reverse Channel can be used as a "busy" or "not ready" indicator.

RxD, TxD and RVC are available at the front panel and USART connector U19 at pins 16, 12, and 14 respectively.

**CAUTION:** If you are using a front panel board connected to U19, make *sure* that it does not make contact with the USART side (pins 9-16). Failure to observe this caution can result in damaged front panel boards and damaged RS232 level shifters. Watch those Imsai front panels!

#### OSCILLATOR SECTION

The oscillator section of the Big Z CPU consists of the following components:

#### A. Main Oscillator Circuit

This consists of crystal Y1, a 4 MHz crystal; inverter U21 (2 sections), capacitors C23, 26 and 27 (0.001 microfarad caps); R10 and R11; and section 1 of U11, a 7474 flipflop. Pin 4 of U21 produces a 4 MHz square wave as the result of the action of the crystal, capacitors, resistors and inverters in the circuit. Flipflop U11 is connected as a divide-by-two circuit. Its Q output, on pin 5, is presented to pin 4 of buffer U29, where is is buffered out to pin 49 of the S-100 bus as CLOCK\*. Its Q\* output, on pin 6, reaches around to its D input, forming the divide-by-two, and is also presented to switch S1 as a 2 MHz signal.

Switch 1 chooses between the 4 MHz signal available from pin 4 of U21, or the 2 MHz signal available as the Q\* of U11.

#### **B. Secondary Oscillator Circuit**

This circuit consists of switch 1, and sections of inverters U15, U21, and U30. The center point of the single-pole double-throw switch S1 receives either a 2 MHz square wave or a 4 MHz square wave, depending on its position. This is fed through inverter U21 (pins 5 and 6) to the Z80 Phi clock input on the CPU pin 6. It is also fed to input pin 13 of inverter U30, exits via pin 12, and is applied to input pin 2 of buffer U29. It passes through buffer U29 which is always enabled by virtue of the fact that its tri-state inputs are grounded, exits at pin 3, and is transmitted to the S-100 bus, pin 24, as the Phi2 clock.

The center point of switch S1 is additionally fed to pin 9 of inverter U21, where it is delayed by the gate-

time of U21, exits via pin 8, and is routed to input pin 13 of inverter U30 through an RC network consisting of C25, a 100 picofarad capacitor, and R12, a 6.8K ohm resistor. This RC network delays the signal by approximately 680 nanoseconds. At inverter U30, the signal is again slightly delayed by the inverter's gate time, exits on pin 10, and is routed to input pin 10 of buffer U29. It passes through the buffer, exits via pin 9, and is transmitted to the S-100 bus on pin 25 as Phi1 clock.

#### **CAUTION:**

Phi1 clock is provided as a convenience only, and is in direct conflict with the IEEE specification of pin 25 as pSTAVAL\*. On IEEE S-100 systems, this clock should be eliminated by cutting the trace between U29 pin 9 and S-100 bus pin 25.

For those cards or systems that require the Phi1 clock signal, this circuitry provides a very good approximation of the actions of an 8080-style 8224 clock driver.

This concludes the Technical Description of the Big Z CPU.

#### THE BIG Z OPTIONS

# OPTION 1-ON-BOARD EPROM

You should have installed the following components: an 8-position switch module at U33, a 24-pin socket at U13, a 16-pin socket at U34, and an 8131 IC at U34.

For a 2708-type EPROM

- Set switch 7 on U33 to OFF.

- 2. Set switch 8 on U33 to ON.

- 3. Select EPROM address from Table A-1 and set the switches on U33 accordingly.

For a TMS 2716-type (TI three-voltage EPROM):

- 1. Install a jumper from A to C.

- 2. Install a jumper from D to B.

- 3. Cut the etch from B to C.

- 4. Set switches 1 and 7 on U33 to ON.

- Set switch 8 on U33 to OFF.

- 6. Select EPROM address from Table A-2 and set the switches on U33 accordingly.

For an Intel-type 2716 (single plus 5 volt only)

- 1. Cut the etch from L to E.

- 2. Cut the etch from F to M.

- 3. Install a jumper from D to M.

- 4. Install a jumper from C to B.

- 5. Install a jumper from I to A.

- 6. Install a jumper from plus 5 volts to E.

- 7. Set switches and 7 on U33 to ON.

- 8. Set switch 8 on U33 to ( ) OFF

- 9. Select EPROM address from Table A-2 and set the switches on U33 accordingly.

For an Intel 2732/TMS 2732 (4K) EPROM:

- 1. Cut the etch from L to E.

- 2. Cut the etch from F to M.

- 3. Cut the etch from G to H.

- 4. Install a jumper from D to M.

- 5. Install a jumper from G to B.

- 5. Install a jumper from C to B.

- 6. Install a jumper from G to E.

- 7. Install a jumper from H to I.

- 8. Set switch 1, 2 and 7 on U33 to ON.

- 9. Set switch 8 of U33 to OFF.

- 10. Select EPROM address from Table A-3 and set the switches on U33 accordingly.

# OPTION 2-M1 WAIT STATE

- 1. Set switch 7 of U23 to OFF.

- 2. Install a jumper from R to F.

- 3. Change USART option to Option 7.

# OPTION 3—1K x 8 Masked ROM (VECTOR GRAPHIC MONITOR)

- 1. Install a jumper from I to A.

- 2. Set switch 1 on U33 to OFF.

- 3. Set switch 8 on U33 to ON.

- 4. Select EPROM address from Table A-1 and set switches on U33 accordingly.

# OPTION 4-NO EPROM AND NO POWER-ON JUMP

Set switch 7 and 8 on U23 to OFF.

#### OPTION 5— POWER-ON JUMP

1. Set switch 8 on U23 to ON.

**NOTE:** an EPROM *must* be on the board to use the Power-On Jump Option. The Big Z CPU will not perform an off-board Power-On Jump.

# OPTION 6—EPROM WAIT STATE (4MHz)

1. Set switch 7 on U23 to ON.

**NOTE:** An EPROM *must* be on the board to use this option.

#### OPTION 7—USART OPTION

You should have installed the following components: an 8-position switch module at U23, a 22 megohm resistor at R6, a 1.8432 MHz crystal at Y2, a 24-pin socket at U2, a 28-pin socket at U3, a 16-pin socket at U24, an 8131 IC at U24, an 8251 IC at U3, a MC14411 IC at U2, an MC1488/75188 IC at U12, a MC1489/75189 IC at U9, the plus and minus 12 volt regulators at VR3 and VR2 respectively, and an 8-position switch module at U1.

1. Set ONE switch on U1 to the desired baud rate. Note that only ONE switch may be on at any given time.

The baud rate is silk-screened next to U1 on the board. All switches other than the one selected must be set OFF.

Select the desired I/O port address from Table A-4 and set the switches on U23 accordingly.

#### OPTION 8-SHADOW EPROM

Enable the Power-On Jump as shown in Option 5.

1. Cut the etch from J to K.

switch positions on U33.

- 2. Install EPROM as shown in Option 1.

- This option is normally used to perform a system boot function. When the system is powered up or reset is activated, the power-on/reset latch formed by U10 is on and the processor will run code from the EPROM. The processor will continue running from the EPROM until a jump occurs to the address range selected by the switches on U33. Note that the program in the EPROM should be assembled to run in an address

range OTHER than the one which is selected by the

When the jump to the selected U33 address range is detected, the EPROM will no longer be accessed, and will be transparent to the system. The program in the EPROM may be assembled to run in any address range as long as that address range is different from the range selected by the switches on U33. The EPROM is accessed for all memory read operations until a memory read is detected that generates an address in the range selected by the switches on U33. At this time, normal memory reads may take place because the power-on/reset latch will be cleared, and normal addressing is restored. I/O instructions and memory writes will execute normally while the power-on/reset latch is set, but all memory reads will address the EPROM.

#### OPTION 9-MRQ\*

Please note that the Memory Request Strobe MREQ, as supplied to the S-100 bus by the Big Z CPU card is a positive true signal. This does not conform with many memory card requirements. If your memory cards require an MRQ\* signal, you can invert MRQ by using one of the spare gates on the board. To do this, tie pins 9 and 10 of U4 high by installing a jumper between these pins and pin 14 (5 volts) of U4. Cut the etch that runs between pin 11 of U17 and pin 65 of the S-100 bus. Install a jumper from pin 11 of U17 to pin 11 of U4. Install a jumper from the output of U4, pin 8, to S-100 bus pin 65. This will give you an inverted MRQ signal. Although the timing of this signal will be slightly delayed, the delay is negligible and should meet the requirements of most any memory board.

# **BOARD ASSEMBLY INSTRUCTIONS**

The JADE BIG Z CPU board is intended for those people who have had some prior experience with kit building and digital electronics. If you do not fall into this category, it is highly recommended that you find an experienced person to help you with the assembly and checkout of the board.

Although there is nothing sacred in the suggested steps that follow, if you will follow them step-by-step you should find your task much easier. We suggest that you start at a time when you will be able to

complete the board. It will help to mark the boxes as

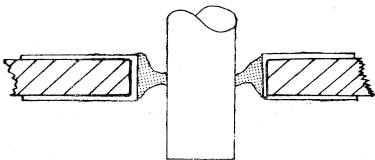

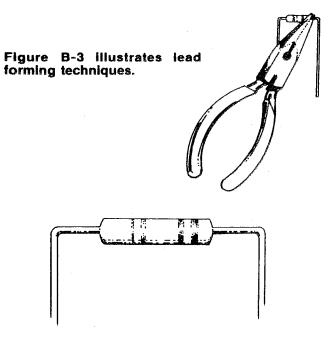

you complete each step. 1. Make sure you have the tools you will need to asemble this kit. For this board you will need the following: a soldering iron (20 watts maximum), Rosin Core solder (preferably 63/37), diagonal cutters, a small magnifying glass, a screwdriver, and a lead former or a pair of needle-nose pliers. 2. Check the parts received against the parts list. Take special care to correctly identify look-alike parts; i.e., resistors, capacitors and diodes. If anything is missing from your kit, please call JADE's Customer Service Department and report the shortage immediately. 3. Read the section of this manual titled "Construction and Soldering Tips." If you have trouble identifying any of the parts, the section titled "Parts Identification" should help you. Do this now before

#### CAUTION

you proceed any further.

# USE EYE PROTECTION WHILE SOLDERING OR CUTTING WIRE

| 4. Install 14-pin sockets at U4, U5, U7, U8, U9,      |

|-------------------------------------------------------|

| U10, U11, U12, U14, U15, U18, U20, U21, U22, U30, and |

| U41. Do not solder them in yet.                       |

| 5. Install 16-pin sockets at U6, U17, U24, U25,       |

| U26, U27, U28, U29, U31, U32, U34, U35, U36, U37,     |

U38, U39, and U40. Do not solder them in yet.

6. Install 24-pin sockets at U2 and U13. Do not solder them in yet.

7. Install 28-pin socket at U3. Do *not* solder it in yet.

8. Install 40-pin socket at U16. Do *not* solder it in yet.

9. A handy trick to help you construct your board is to insert all the above sockets into the board first, then place the flat styrofoam cover you received with your kit box firmly against the top of the board. Turn it over, holding the flat styrofoam piece tightly against the board. The IC sockets should not be on the bottom. Press the board down, forcing the sockets into the styrofoam. Now solder alternating corner pins of the IC sockets to hold them in place temporarily (pins 8 and 16 on a 16-pin socket, for instance.)

Now turn the board over and very carefully inspect it to determine that all the IC sockets are down flat against the board. If you find any that aren't down flat, melt the solder joints at the corners of the IC socket and press it down against the board.

When you have determined that all the IC sockets are down firmly on the board, turn the board back over and solder all the pins. Make sure that all the pins are sticking through the board. IC sockets are very difficult to remove once they are soldered onto a board. For soldering hints, turn to Appendix B of this manual.

10. Install 1.5 ufd capacitors at C16 through C21. (NOTE that there are *two* C17s on the board. This is to allow you a choice between using dip tantalum caps and radial electrolytics. Dip tantalums are much preferable and are the type shipped with the Big Z kits as supplied by **JADE**. Install C17 according to the type of capacitor you are using.)

11. Install 0.1 ufd capacitors at C1 through C15.

12. Install the three DIP switches at U1, U23, and U33. Do not place these DIP switches in sockets—they are liable to fall out under use.

| 13. Install a 100 microfarad electrolytic capacitor at C22.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | solder side of the board, with the nut next to the regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14. Install a 100 picofarad capacitor at C24 and C25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25. Check all your solder joints carefully. Inspect the board for cold solder joints or solder                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15. Install a 0.001 ufd capacitor at C23, C26, and C27.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bridges, as per the instructions in Appendix B.  26. <b>BEFORE INSTALLING ANY ICs</b> —place                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16. Install a 330 ohm resistor (orange, orange, brown) at R5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | the board in your computer and check all the voltages to make sure that you do not have any power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17. Install the 1K ohm resistors (brown, black, red) at R4, R10, and R11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | shorts on the board. The output voltages from all the regulators can be measured on the pin facing toward the top of the board (away from the S-100 connector).                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18. Install a 2.7K ohm resistor (red, violet, red) at R2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Be careful not to let your probes short the voltage regulator pins together, since this can destroy a                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 19. Install the 4.7K ohm resistors (yellow, violet, red) at R1, R3, R7, R8, R9, R13 and R14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | voltage regulator very neatly—and quickly. If all of the voltages are up to par (plus or minus about half a volt or so), continue to step 27; otherwise, check the board                                                                                                                                                                                                                                                                                                                                                                                            |

| 20. Install the 6.8K ohm resistors (blue, gray, red), at R12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | again for shorts. Find that short before you install any ICs, and correct it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 21. Install the 22 megohm resistor (red, red, blue) at R6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27. Install all ICs and resistor packs in the locations shown on the Assembly Drawing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul><li>22. Install a 4 MHz crystal at Y1.</li><li>23. Install a 1.8432 MHz crystal at Y2.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28. Install whatever options you have chosen from the Options list.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 24. Install the voltage regulators. The 7805/LM340T5 regulator is installed at VR4. This is the plus 5 volt regulator and should be used with a heat sink. If you have a good heat sink compound, we suggest you use it at this regulator only. Use it sparingly, as too much is worse than none at all. Now install the 7912/LM320T12 regulator (minus 12 volts) at VR2. Install the 7905/LM320T5 (minus 5 volts) regulator at VR1. Install the 7812/LM340T12 (plus 12 volts) regulator at VR3. Button them down with the screws and nuts supplied. Place the screw through the | 29. Install a single-pole double-throw switch at T-U-V. If a switch has not been included in your kit, solder in the wire-wrap pins in its place. The center to top hole (T to U) selects a 2 MHz clock. The center to bottom hole (U to V) selects a 4 MHz clock. Regardless of the switch setting, the CLOCK* signal on pin 49 of the S-100 bus will be 2 MHz, as per IEEE specifications.  30. You should now be on the air. If you have trouble, go to the "Troubleshooting Tips" section of this manual for checkout procedures. If you don't—happy computing! |

# CHECKOUT PROCEDURES AND TROUBLESHOOTING TIPS

Before plugging the board into the sytem, do the following:

- 1. Carefully inspect the board for solder shorts or damaged components.

- 2. Insure that all ICs are out of their sockets at this point.

- 3. Install all options that are to be used in your system. Be especially careful when installing EPROM options, because your EPROM may be permanently damaged by improper jumper configurations. Five-volt-only EPROMS can be destroyed by the minus 5 and plus 12 volts supplied to the EPROM socket if the etches are not properly cut. Ohm them out before

installing the EPROM, or check the voltages at the proper socket pins.

Some confusion can exist for parts labeled 2716. Texas Instrument parts use plus 12 and minus five volts, while others (such as Intel), are five-volt-only types. The Texas Instrument TMS2516 is a five-volt-only part that is identical to the Intel 2716.

4. Plug the processor board into the bus with power OFF, being careful to line up pins 50 and 100 with the ground pins on the bus. If the board should somehow inadvertently become reversed in the S-100 connector, extensive damage could result when power is applied. In most mainframes, it is physically impossible to insert the card backwards—but some

people have managed to do it. It never hurts to make sure, and we'd rather insult your intelligence by telling you about it than see you destroy your CPU card.

- 5. It is highly recommended that the plus five volt supply be monitored while applying power for the first time. Shut the system down *immediately* if the supply does not read five volts (plus or minus something really reasonable). Monitor the other voltages as well before attempting to run the processor in the system.

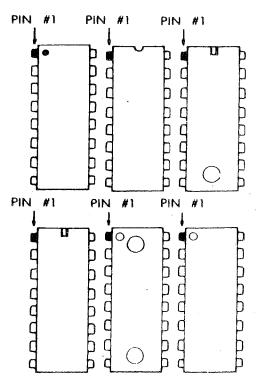

- 6. Next, install all the ICs in their sockets according to the parts list or the assembly drawing. Make certain that pin one of all ICs are down, facing the S-100 bus connector on the board. There is no exception to this rule—all ICs face the bottom of the board. If you are not sure where pin 1 is on an IC, refer to the parts identification section of this manual.

- 7. Carefully turn the power on. Check for any discoloration in the parts and touch each IC gingerly. If it is very hot, chances are that you have inserted it backwards. Remove it, throw it away, and install a new part. The old one might work, but it is bound to fail in the near future, and according to Murphy's Law, which states that darn near anything can happen bad, it will fail exactly when you are most depending on it, like in a 14-hour sort or something. (Editor's Note: JADE's corollary to Murphy's Law states that "Murphy was an optimist!")

If you have a front panel, single-step the board to see if the first few instructions are fetched properly. In case of problems, carefully check all options installations and switch settings, since this is the most common cause of difficulty with this board.

Please note that not all front panel boards will work with the **Big Z** CPU card. Since the Big Z was designed to conform as much as possible with the proposed IEEE S-100 standard, it does not provide mirrored I/O addressing. Mirrored I/O addressing is an old Imsai/80890 convention in which the I/O address is mirrored (carried by both the upper and lower halves of the address bus). With the advent of the Z80 CPU, it became possible to perform block I/O instructions. The Z80 uses the upper half of the address bus to provide a byte count to its peripherals during these block move I/O instructions, and the use of mirrored I/O addressing effectively precludes this entire class of very useful instruction from the Z80's reportoire.

Some board designers (heaven only knows why) decode the upper half of the address bus for an I/O address. Why? We've never been able to figure it out. Among these that we know about are the Vector Graphic Flashwriters and I/O cards, Imsai front panel boards, Imsai I/O boards, the MECA tape system, Computime clock and calculator boards, and others.

Although the IEEE does not specifically forbid this practice, it is strongly discouraged. The designers of

the Big Z CPU have elected not to implement mirrored I/O addressing. If you have cards which use this addressing scheme, we suggest that they be modified to decode the *lower* half of the address bus (A0-A7) rather than the upper half.

One of the most common problems we have encountered with our customers using the Big Z is caused by the EPROM not being properly accessed after a power-on or reset. If the EPROM you are using has a paper label over the window, do not assume that it is a 2708 or other EPROM. Carefully lift the label to see if a transparent window is present on the device. If no window is present, it is a masked ROM or PROM. ROMs and PROMs that have pinouts similar to the 2708 or 2716 will work on the Big Z provided that you insure that pins 18, 19, 20 and 21 of the device are supplied with the same voltages as in the circuit in which they were originally used.

Instructions are included in the Options section for interfacing a Vector Graphics Monitor ROM. Note that the ROM, PROM or EPROM that is the starting point of the system monitor or bootstrap loader must be located on the Big Z CPU board in order to use the power-on jump feature. Devices that form the remainder of the system monitor may reside on other boards in the system, but the starting point of the monitor must by on the processor board.

Tarbell disk controllers that use an on-board coldstart loader ROM will not work with the Big Z. JADE has available several monitor ROMs that include the Tarbell disk interface cold-start loader routines. The on-board ROM on the Tarbell controller must be disabled.

To continue the checkout procedure:

- 8. If the voltages you have monitored during steps 5 and 7 have not been up to par, either the regulators are defective (most unlikely), or a short circuit exists somewhere on the board. Power down and check for solder bridges.

- 9. Check Z80 pin 6 for a 2 or 4 MHz square wave. If this is not present, you have trouble in the Oscillator section of the board. Check the ICs. Check the capacitors and resistors for proper values. Check for solder bridges or shorts.

- 10. Halt the CPU. Hold the reset button down and look at the following pins of the Z80 with a voltmeter or preferably a logic probe or oscilloscope:

pin 26 (RESET\*) should be LOW. pins 1-5 and 30-40 (A0-A15) should be HIGH. pins 7-10 and 12-15 (D0-D7) should be HIGH.

Now release the RESET button. Look at the following pins on the Z80:

pin 26 (RESET\*) should be HIGH. pin 25 (BUSRQ\*) should be HIGH.

pin 24 (WAIT\*) should be LOW. pin 18 (HLTA\*) should be HIGH. pin 27 (M1\*) should be LOW. pin 16 (INT\*) should be HIGH. pin 17 (NMI\*) should be HIGH. pin 23 (BUSAK\*) should be HIGH. A0-A15 should be LOW.

- 11. Install a monitor EPROM. Hit reset. Examine pin 9 of comparator U34. You should see a low-going pulse as the EPROM is selected. If pin 9 remains high, you have probably addressed your switches incorrectly. Check them out against the proper settings on the applicable Table A section for your type of EPROM. If pin 9 remains low, either there is something wrong with the address lines of the internal address bus, or the comparator is defective, or U10 is defective. Make sure you have the pullup resistor packs and pullup resistors properly installed.

- 12. With an EPROM installed, check pin 9 of comparator U24 to determine if the USART is being addressed correctly. Follow the same logic as in step 11 above.

- 13. Check your monitor program against the sample monitor program included with this manual. You may have a software problem. The most common software problem we have encountered centers around incorrect initialization of the 8251 USART.

#### PROGRAMMING THE USART

A simple program that uses the USART as output is included with this manual. Note that the RS232C interface from the USART is contained on the same DIP connector as the front panel signals. When connecting a front panel, be careful to insure that the RS232 levels do not go to any circuitry on the front panel through the DIP connector cable. This could render the USART unusable, as well as damage components on the front panel board. The DIP cable will have to be split at the DIP connector if a front panel is used in conjunction with the RS232 interface. A cable from pins 1 through 8 will go to the front panel. A cable from pins 9 through 16 will go to the RS232 connector or plug.

The USART appears as two consecutive port I/O addresses to the processor. U24 decodes a group of four consecutive addresses and the two lower addresses of this group of four are enabled by A1 going low at pin 12 of U14. The upper two addresses may be enabled to talk to the USART by cutting the etch on the solder side of the board at U14, pin 12.

An ODD address (i.e., A0 is 1 or high) selects the USART command/status register and an EVEN

address (i.e., A0 is 0 or low) selects the USART data register. After a power-on or reset, the USART must be programmed (initialized) for use by outputting a mode word, followed by a command word. The format for the mode word is as follows:

Bit 0 0

Bit 1 1

Bits 2 & 3:

00 means 5 bits per character.

10 means 6 bits per character.

01 means 7 bits per character.

11 means 8 bits per character (most usual configuration)

Bit 4—0 means parity disabled, 1 means parity enabled.

Bit 5—0 means odd parity selected, 1 means even parity selected.

Bits 6 & 7:

00 is an invalid, illegal combination.

01 means one and one-half stop bits.

10 means one stop bit (most usual configuration).

11 means 2 stop bits (usually used at 300 baud or less).

After writing the mode word, a slight delay is needed before writing the command word. This word can be sent to the USART after a LD A instruction, which will provide the necessary delay, and is required anyway. The command word is written to control the transmit or receive function of the USART. The functional format for the command word is as follows:

Initiate Transmit is 33 hex.

Initiate Receive is 36 hex.

Reset is 40 hex (same as a power-on condition). Initiate both transmit and receive is 37 hex.

The mode and command words are only written once after a power-on or reset is performed. The command word may be written each time the function is to change or be selected. Note that this is not necessary when the command word sent to the USART is 37 hex—both transmit and receive are enabled.

The status register of the USART is obtained from inputting the command register. The format of the status register is as follows:

Bit 0. When this bit is high, it means that the Transmitter Buffer is empty and the USART is ready for another data character. This bit is reset by outputting a character to the USART's data register.

Bit 1. When this bit is high it means that a character has been received and assembled by the USART (data is available). This bit is reset when the character is input from the data register of the USART.

Bit 2. When this bit is high, it means that the transmitter is enabled and the USART is in its Transmit Mode.

Bit 3. When this bit is high, it means that the USART has detected a parity error in the character it has just received, or transmitted.

Bit 4. When this bit is high, it signals an Overrun Error. This means that the received data was not input from the USART by the CPU soon enough to allow the USART to properly receive and assemble the next character.

Bit 5. When this bit is high, it signifies a Framing Error. A framing error means that an improper stop bit was detected at the end of the character. This condition can be caused by transmitting the wrong number of data bits or by the wrong baud rate being selected.

Bit 6 is not used, and its condition is meaningless. Bit 7. When this bit is high, it means Reverse Channel. This is used for a "buffer full" or "not ready" indication from peripheral devices. It can be active high or low, depending on the device. A TTL-level signal may be used at the RS232 interface is an RS232 signal is not available.

The following software example sets the mode word to select 8 bits per character, no parity, and 1 stop bit. The system should have been powered-on or reset just prior to executing this program. The command word that is output next selects the transmit and receive mode. The status is read and bit 0 is tested to see if the USART is ready for a character. If this bit is high, then a 55 hex (ASCII "U") is output as a character. The program then loops, testing the status, and transmits a continuous string of "U's". If the transmit data is viewed with an oscilloscope, it appears as a square wave with the low or high portions equal to the bit time or baud rate. The reciprocal of the baud rate will give the bit time in seconds. For example, 1/600 baud equals 1.667 milliseconds (0.001667 seconds).

#### 'USART SOFTWARE EXAMPLE'

| ADDR     | CODE | STMT SOURCE  | STATEMENT   |                                |

|----------|------|--------------|-------------|--------------------------------|

|          |      | 0002 ;       |             |                                |

|          |      | 0002 4       | PSECT AL    | a <b>B</b> S                   |

| >0100    |      | 0003         |             | 0100H                          |

|          |      | 0005 ;       | ono o       | TOOH                           |

|          |      | 0006 ;       | dofine eve  | mbols used                     |

|          |      | 0007 ;       | deline si   | WID012 0260                    |

| >0011    |      | 0008 SSTAT   | EQU 1:      | 1H                             |

| 00010    |      | 0009 SDATA   |             | OH                             |

| >0001    |      | 0010 TXRDY   |             | 21H                            |

|          | •    | 0011 ;       |             |                                |

|          |      | 0012 ;       |             |                                |

| 0100     | BE4E | 0013 PGM:    | LD A        | 1,4EH :mode word               |

| 0102     | D311 | 0014         |             | SSTAT),A                       |

|          |      | 0015 sout to |             |                                |

| 0104     | 3E37 | 0016         |             | 37H scommand word              |

|          |      | 0017 ;enable |             | nsmit and receive              |

|          |      | 0018 ;modes  |             |                                |

| 0106     | D311 | 0019         | OUT (S      | SSTAT),A                       |

| >0108    |      | 0020 LOOP:   |             |                                |

| 0108     | DB11 | 0021         | IN A        | ,(SSTAT)                       |